Judy L. Hoyt

Collaborators

- D. Antoniadis, EECS

- F. Kartner, EECS

- M. Canonico, ASU

- T. Lyszczarz, MIT Lincoln Labs

- J. Yoon, MIT Lincoln Labs

- A. Nayfeh, Masdar Institute

Graduate Students

- W. Chern, EECS

- N. DiLello, EECS

- L. Gomez, EECS

- M. Kim, DMSE

- J. Teherani, EECS

Research Staff

- G. Riggott, Research Specialist

- P. Hashemi, Post-doctoral Scholar

Support Staff

- W. Rokui, Admin. Asst. II

Publications

P. Hashemi, J.T. Teherani, and J.L. Hoyt, “Investigation of Hole Mobility in Gate-All-Around Si Nanowire p-MOSFETs with High-k/Metal-Gate: Effects of Hydrogen Thermal Annealing and Nanowire Shape,” International Electron Device Meeting (IEDM 2010), San Francisco, USA, Session 34.5 December 2010.

P. Hashemi, C.D. Poweleit, M. Canonico, and J.L. Hoyt, “Advanced Strained-Silicon and Core-Shell Si/Si1-xGex Nanowires for CMOS Transport Enhancement,” ECS (Electrochemical Society) Transactions, October 2010.

M. Kim, P. Hashemi, and J.L. Hoyt, Increased critical success for high Ge-content strained SiGe-on Si Using selective epitaxial growth, Appl. Phys. Lett. 97, 262106, 2010.

L. Gomez, C. Ni Chleirigh, P. Hashemi, and J.L. Hoyt, “Enhanced Hole Mobility in High-Ge Content Asymmetrically Strained-SiGe p-MOSFETs,” IEEE Electron Device Letters, vol. 31, no. 8, pp. 782 – 784, August, 2010.

Guangrui Xia and J.L. Hoyt, “Si-Ge interdiffusion under oxidizing conditions in epitaxial SiGe heterostructures with high compressive stress,” Applied Physics Letters, v 96, n 12, p 122107 (3 pp.), 22 March 2010.

P. Hashemi, M. Kim, J. Hennessy, L. Gomez, D.A. Antoniadis and J.L. Hoyt, “Width-dependent hole mobility in top-down fabricated Si-core/Ge-shell nanowire MOSFETs”, Appl. Phys. Lett. 96 (6), p. 063109, Feb. 2010.

J.S. Orcutt, A. Khilo, M.A. Popovic, C.W. Holzwarth, H. Li, J. Sun, B. Moss, M.S. Dahlem, E.P. Ippen, J.L. Hoyt, V. Stojanovic, F.X. Kärtner, H.I. Smith, and R.J. Ram, “Photonic integration in a commercial scaled bulk-CMOS process,” Source: 2009 International Conference on Photonics in Switching, PS ’09, 2009, 2009 International Conference on Photonics in Switching, PS ’09, p. 2.

L. Gomez, P. Hashemi, and J.L. Hoyt, “Enhanced Hole Transport in Short-Channel Strained-SiGe p-MOSFETs,” IEEE Transactions on Electron Devices, vol. 56, no.11, pp.2644-2651, Nov. 2009.

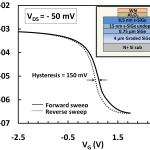

O.M. Nayfeh, J.L. Hoyt and D.A. Antoniadis, “Strained Si1-xGex/Si Band-to-Band Tunneling Transistors: Impact of Tunnel-Junction Germanium Composition and Doping Concentration on Switching Behavior,” IEEE Transactions on Electron Devices, vol. 56, no. 10, pp. 2264-2669, Oct. 2009.

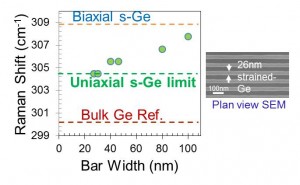

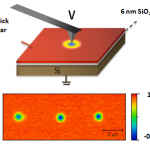

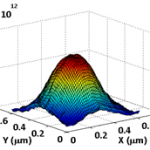

P. Hashemi, L. Gomez, and J.L. Hoyt, “Gate-All-Around N-MOSFETs with Uniaxial Tensile Strain-Induced Performance Enhancement Scalable to Sub-10-nm Nanowire Diameter,” IEEE Electron Device Letters, vol. 30, no. 4, pp. 401-403, April 2009.

A.K. Sood, R.A. Richwine, Y.R. Puri, N. DiLello, J.L. Hoyt, T.I. Akinwande, S. Horn, R.S. Balcerak, G. Bulman, R. Venkatasubramanian, R., A.I. D’Souza, T.G. Bramhall, “Development of low dark current SiGe-detector arrays for visible-NIR imaging sensor,” Proceedings of the SPIE, vol. 7298, p 72983D, 2009.

C. Batten, A. Joshi, J. Orcutt, A. Khilo, B. Moss, C. Holzwarth, M.A. Popovic, Hanqing Li, H.I. Smith, J.L. Hoyt, F.X. Kartner, R.J. Ram, V. Stojanovic, and K. Asanovic, “Building many-core processor-to-DRAM networks with monolithic CMOS silicon photonics,” IEEE Micro, vol. 29, no. 4, pp. 8-21, July-Aug. 2009.

C.W. Holzwarth, et al., “High speed analog-to-digital conversion with silicon photonics,” Proceedings of the SPIE v 7220, p 72200B (15 pp.), 2009.

L. Gomez, P. Hashemi, and J.L. Hoyt, “Enhanced Hole Transport in Short-Channel Strained-SiGe p-MOSFETs,” IEEE Transactions on Electron Devices, vol. 56, no. 11, pp. 2644-2651, Nov. 2009.

O.M. Nayfeh, J.L. Hoyt and D.A. Antoniadis, “Strained Si1-xGex/Si Band-to-Band Tunneling Transistors: Impact of Tunnel-Junction Germanium Composition and Doping Concentration on Switching Behavior,” IEEE Transactions on Electron Devices, vol. 56, no. 10, pp. 2264-2669, Oct. 2009.

P. Hashemi, L. Gomez, and J.L. Hoyt, “Gate-All-Around N-MOSFETs with Uniaxial Tensile Strain-Induced Performance Enhancement Scalable to Sub-10-nm Nanowire Diameter,” IEEE Electron Device Letters, vol. 30, no. 4, pp. 401-403, April 2009.