A 93% Efficiency Reconfigurable Switched-Capacitor DC-DC Converter Using On-Chip Ferroelectric Capacitors

- Category: Circuits & Systems

- Tags: anantha chandrakasan, dina el-damak, saurav bandyopadhyay

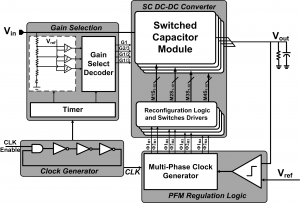

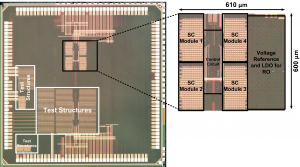

Switched-Capacitor (SC) DC-DC converters have gained significant interest as promising candidates for integrated power conversion solution that eliminates the need for inductors. However, SC converters efficiency is limited by the conduction loss, bottom plate parasitic capacitance, and gate drive loss in addition to the overhead of the control circuits. In this work, we exploit on-chip ferroelectric capacitors (FeCaps) for charge transfer owing to their high density and extremely low bottom plate parasitic capacitance. High-efficiency conversion is achieved by combining the FeCaps with multi-gain setting converter in a reconfigurable architecture with dynamic gain selection. Figure 1 shows the top-level architecture of the system which consists of a reconfigurable switched capacitor DC-DC converter split in four interleaved modules for output voltage ripple reduction, pulse frequency modulation (PFM) logic, a clock generator, gain selection block that includes programmable low duty cycle timers, and a voltage reference. The PFM modulation scheme is performed using a dynamic comparator whose output is fed into cascaded clock dividers, after which non-overlap clock generators to provide the multi-phase control signals. The SC converter gain setting is selected based on the ratio of the reference to the input voltage by using dynamic comparators and gain select decoder to set the configuration of the switch matrix. The system was fabricated in 130-nm CMOS process and occupies an area of 600×610 μm2 as shown in Figure 2. The converter supports four conversion ratios (1/3-1/2-2/3-1) while supplying a wide output voltage range of 0.4V to 1.1V from 1.5V input and a load current of 20μA to 1mA. The system achieves a peak efficiency of 93% including the control overhead at load current of 500µA and output voltage of 0.96V while the SC DC-DC converter alone achieves a peak efficiency of 94%.

- Figure 1: System top-level architecture

- Figure 2: Chip micrograph.