Two-stage Power Conversion Architecture for an LED Driver Circuit

- Category: Circuits & Systems

- Tags: david perreault, sengbum lim

LED lighting promises unprecedented reductions in energy consumption, but it comes with an as-yet unmet demand for high power density, high efficiency, and high-power-factor LED drivers[1]. Considering a group of commercial line-interfaced LED drivers in the output power range of 3-30 W, we have found efficiencies in the range of 64-83% and power factors of 0.59-0.96, with no systems achieving both high efficiency and a high power factor. The switching frequencies of these drivers were in the range of 57-104 kHz, with correspondingly low power densities below 5 W/in3. The size of these drivers was uniformly dominated by magnetic components, and in each case the driver represented a major contribution to overall system size. It may be concluded that power conversion electronics continue to represent a major limitation in solid-state lighting, and that significant improvements in driver efficiency, power density and power factor will be necessary to meet market needs.

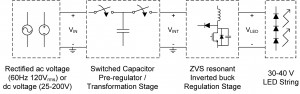

We introduce a merged-two-stage circuit topology and associated circuit design and controls to address these challenges. The proposed approach is suitable for efficient LED drivers operating from either a wide-range dc input voltage or an ac line voltage. This two-stage topology is based on a soft-charged switched-capacitor pre-regulator/transformation stage and a high-frequency magnetic regulator stage. Soft charging in the switched capacitor circuit, zero voltage switching in the high-frequency regulator circuit, and time-scale controls are used to maintain high efficiency, high power density, and a high power factor. Two implementations of the proposed architecture are demonstrated: a wide input voltage range dc-dc converter and a line interfaced ac-dc converter. The dc-dc converter shows 85-95% efficiency at 20W power across 25-200V input voltage range, and the ac-dc converter achieves 88% efficiency with 0.93 power factor at 8.4W average power[2][3][4][5][6][7][8].

- Figure 1: Block diagram of the merged-two-stage conversion system.ottom): 100mA/div).

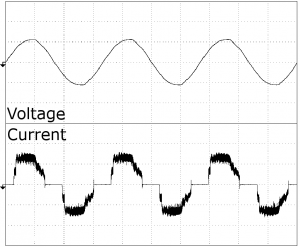

- Figure 2: Experimental measurement of input voltage and current waveforms from ac-line operation line (x: 5ms/div (top): 150V/div, (bottom): 100mA/div).

- “Multi-year program plan fy09-fy14: Solid-state lighting research and development,” Office of Energy Efficiency and Renewable Energy, US Dept. of Energy by Navigant Consulting, Radcliffe Advisors, and SSLS, 2008. [↩]

- D. Perreault, J. Hu, J. Rivas, Y. Han, O. Leitermann, R. Pilawa-Podgurski, A. Sagneri, and C. Sullivan, “Opportunities and challenges in very high frequency power conversion,” in Applied Power Electronics Conference and Exposition, APEC 2009. Feb. 2009, pp. 1 –14. [↩]

- J. Hu, “Design of low-voltage, high-bandwidth radio-frequency power converters,” Ph.D. dissertation, Massachusetts Institute of Technology, Cambridge, 2012. [↩]

- M. Seeman and S. Sanders, “Analysis and optimization of switched capacitor dc-dc converters,” Power Electronics, IEEE Transactions on, vol. 23, no. 2, pp. 841 –851, Mar. 2008. [↩]

- R. Pilawa-Podgurski, D. Giuliano, and D. Perreault, “Merged two stage power converter architecture with soft charging switched-capacitor energy transfer,” in 39th IEEE Power Electronics Specialists Conference, 2008. [↩]

- R. Pilawa-Podgurski and D. Perreault, “Merged two-stage power converter with soft charging switched-capacitor stage in 180 nm CMOS,” IEEE Journal of Solid-State Circuits, vol. 47, no. 7, pp. 1557-1567, 2012. [↩]

- R. Pilawa-Podgurski and D. Perreault, “Merged two-stage power converter with soft charging switched-capacitor stage in 180 nm CMOS,” in ESSCIRC 2011, Sept. 2011, pp. 479–482. [↩]

- M. Seeman and S. Sanders, “Analysis and optimization of switched capacitor dc-dc converters,” in IEEE Computers in Power Electronics Workshop, 16-19 July 2006, pp. 216–224. [↩]