Low-power Memory Circuits

- Category: Circuits & Systems, Energy

- Tags: anantha chandrakasan, yildiz sinangil

Transistor scaling has resulted in integration of more functionality on a single die. On-chip memories are responsible for a large portion of the system power, and low-voltage memory design is an important research topic[1]. Starting at 45 nm, different process technologies are investigated to achieve low-voltage memory operation. Early silicon data predict that at a 22-nm node, 6T SRAM macros on FD-SOI can reach 6-sigma yield at VDD as low as 0.6V.

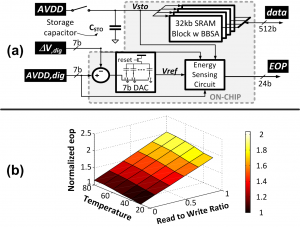

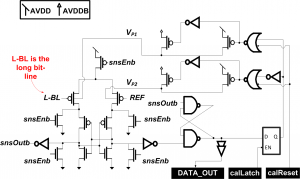

With continuous scaling, systems are getting more complex. Those complex systems usually need to meet multiple constraints and must be optimized for achieving conflicting goals. Additionally, they must perform efficiently under dynamically changing conditions. Self-aware systems can be used to achieve better system optimization by utilizing run time monitoring of critical system metrics[2]. Figure 1-b shows measured EOP calculated by our on-chip energy sensing circuit across different temperatures and by varying total read and write operation ratios. Depending on these conditions, EOP can change by more than 2×. Thus, an energy sensing circuit that generates a digital representation of absolute energy per operation (EOP) consumed by the caches would provide useful information to the system. Moreover, memories often limit system performance. To address this trait, we use a novel body-biased sense amplifier in our SRAM (BBSA) (Figure 2). In BBSA we propose an offset compensation technique using body-biasing to reduce input-referred offset of sense-amplifiers. BBSA can achieve a 1.9× smaller input offset voltage by using AVDDB = AVDD + 150 mV.

The block diagram of our 128-kbit SRAM with embedded energy sensing circuit is given in Figure 1-a[3]. SRAMs are designed using an 8T bit-cell and can operate down to 0.37 V. In addition, an on-chip energy metering circuit measures run time absolute energy per operation numbers of the SRAM blocks. Active power consumed by energy sensing circuit is 0.28% of the SRAM active power. The small area and power overhead of the energy sensing circuit makes it suitable for system-level power management.

- Figure 1: (a) Chip block diagram. (b) Measured EOP under different read operation to write operation ratios and temperatures. EOP changes by more than 2× across different conditions.

- Figure 2: Body-biased sense amplifier circuit diagram. BBSA utilizes body biasing to reduce input-referred offset voltage of its input transistors (M1 and M2) by controlling their body voltages (VP1 and VP2). M3 to M6 PMOS transistors drive VP1 and VP2 to either AVDD or AVDDB depending on the outcome of the calibration process.

- N. Ickes, Y. Sinangil, F. Pappalardo, E. Guidetti, and A. P. Chandrakasan, “A 10 pJ/cycle ultra-low-voltage 32-bit microprocessor system-on–chip,” ESSCIRC, pp. 159-162, Sep. 2011. [↩]

- H. Hoffmann, J. Holt, G. Kurian, E. Lau, M. Maggio, J. E. Miller, S. M. Neuman, M. Sinangil, Y. Sinangil, A. Agarwal, A. P. Chandrakasan, and S. Devadas, “Self-aware Computing in the Angstrom Processor,” Proceedings of the 49th Design Automation Conference (DAC), June 2012. [↩]

- Y. Sinangil and A. P. Chandrakasan, “An Embedded Energy Monitoring Circuit for a 128kbit SRAM with Body-biased Sense-Amplifiers,” A-SSCC, Nov. 2012. [↩]