Beyond Equalization: Model Predictive Control

- Category: Circuits & Systems

- Tags: amr suleiman, vladimir stojanovic

As CMOS technology scales down and the need for higher data rates increases, non-ideal channel characteristics play a critical role in limiting the speed. Equalization is a well-known method to overcome band-limited channels and reflections[1]. Most high-speed links apply transmitter equalization using a finite impulse response feed forward equalizer (FFE), with an optional decision feedback equalizer (DFE) at the receiver[2],[3].

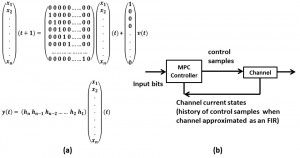

This work proposes a new nonlinear equalization method using a model predictive control (MPC) algorithm. MPC is a class of control algorithms in which the current control action is obtained by solving online, perhaps approximately, an open-loop optimal control problem. One important advantage of MPC in peak-power constrained link environment is its ability to cope with hard constraints on controls and states[4]. Figure 1 shows how this algorithm is used; the channel is modeled as an FIR (Figure 1a) filter, which enables feeding back channel states to the MPC controller to solve the optimization problem (Figure 1b). Knowing the state of the channel enables a very fine nonlinear equalization.

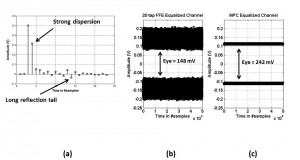

MPC equalization significantly outperforms traditional FIR-based equalizers by more than 63% increase in eye opening height as shown in figure 2. Interestingly, the more the channel is dispersed in time and suffers from reflections, the more improvement MPC can achieve. The complexity of this algorithm is the main challenge in implementations; however, techniques can be applied to design hardware MPC equalizers with reasonable area and power budgets, by sacrificing some performance gains. The main candidate is a RAM-DAC implementation[5], which can achieve equalization and compensate for any timing mismatches or DAC non-linearity.

- Figure 1: Modeling the equalization problem: (a) channel state-space representation, (b) block diagram for MPC algorithm. Note that the MPC controller is a function of input bits (horizon) and channel current state.

- Figure 2: (a) Pulse response of 3 inches backplane channel @ 8 Gbps[6] . (b) Channel output with 20-tap FIR equalizer. (c) Channel output with MPC equalizer.

- J. Liu and X. Lin, “Equalization in high-speed communication systems,” IEEE Circuits and Systems Magazine, vol. 4, no. 2, pp. 4- 17, 2004. [↩]

- V. Stojanovic and M. Horowitz, “Modeling and analysis of high-speed links,” in Proceedings of the IEEE Custom Integrated Circuits Conference, pp. 589- 594, 2003. [↩]

- A. Agrawal, J. Bulzacchelli, T. Dickson, Y. Liu, J. Tierno, and D. Friedman, “A 19Gb/s serial link receiver with both 4-tap FFE and 5-tap DFE functions in 45nm SOI CMOS,” in Proceedings of the IEEE International Solid-State Circuits Conference, pp. 134-136, Feb. 2012. [↩]

- J-S. Zhou, Z-Y. Liu, and R. Pei, “A new nonlinear model predictive control scheme for discrete-time system based on sliding mode control,” Proceedings of the 2001 American Control Conference, vol. 4, pp. 3079-3084, 2001. [↩]

- R. Sredojević and V. Stojanović, “Fully Digital Transmit Equalizer With Dynamic Impedance Modulation,” IEEE Journal of Solid-State Circuits, vol. 46, no. 8, pp. 1857-1869, Aug. 2011. [↩]

- W. Peters, E. Gong, C. Chen, and H. Kim, “Improved HVM ATCA measurement data,” http://www.ieee802.org/3/ap/public/channel_model/peters_m1_0605.zip, July 2005. [↩]