Time-interleaved A/D Converters

- Category: Circuits & Systems

- Tags: daniel kumar, hae-seung lee

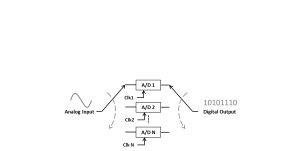

There is an ever-increasing demand for high-resolution and high-accuracy A/D converters in communication systems. In order to raise the sampling rates to the GHz range in a power efficient manner, time-interleaving is an essential technique whereby N A/D channels, each operating at a sampling frequency fs, are used to achieve an effective conversion speed of Nfs, as illustrated in Figure 1.

While time-interleaving enables higher conversion rates in a given technology, mismatch issues such as gain, offset, and sampling clock skew errors between channels degrade the overall A/D performance[1]. Of these issues, sampling clock skew between channels is the biggest problem in high-speed and high-resolution, time-interleaved A/D. There are a few sources of sampling clock skew between channels. Mismatches in the sampling clock path and logic delays are the most obvious. Input signal routing mismatch and RC mismatch of the input sampling circuits also cause sampling clock skew. Previous calibration techniques employ either analog and digital timing adjustment or digital calibration of output data. The timing adjustment requires adjustable delay resulting in increased sampling jitter, which cannot be compensated by calibration. The digital calibration of output data requires complex interpolation.

In this research, we are developing a simpler calibration algorithm for sampling clock skew correction whereby the input signal is delayed by controlling the resistance of the input sampling switch. The variable time-constant of the input sampling network will result in a linear delay of the input signal if the RC time constant of the input sampling network is much greater than 1/fin, where fin is the input signal frequency. This sampling method allows for finely tuned timing-skew corrections, and the impact on noise or power consumption of the system is negligible. A 12-b, 240MS/s, 4-way time-interleaved A/D is being taped-out to demonstrate the new calibration scheme.

- N. Kurosawa, H. Kobayashi, K. Maruyama, H. Sugawara, and K. Kobayashi, “Explicit analysis of channel mismatch effects in time-interleaved ADC systems,” IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 48, no. 3, pp. 261-271, Mar. 2001. [↩]