Low-power High-performance SAR ADC with Redundancy and Digital Background Calibration

- Category: Circuits & Systems, Medical Electronics

- Tags: albert chang, duane boning, hae-seung lee

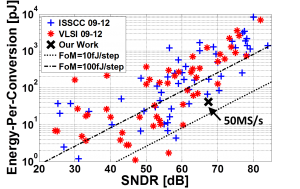

Figure 1: Comparison with the state-of-the-art (data adopted from B. Murmann, “ADC Performance Survey 1997-2012,” http://www. stanford.edu/~murmann/adcsurvey.html).

A. H. Chang, H.-S. Lee, D. S. Boning

Sponsorship: Masdar Institute of Science and Technology

There is a growing demand for low-power, high-speed and high-resolution A/D converters for applications such as wideband wired/wireless communication, software radio and millimeter-wave imaging systems. For many years, the successive-approximation-register (SAR) ADC has appeared mostly in the low-speed and low-power applications. The unprecedented improvement in speed and energy efficiency of scaled CMOS technologies helps expand the SAR architecture into the median-to-high-speed application domains that are traditionally designed using the flash or pipelined architectures. Along with other benefits, such as good digital compatibility, excellent power, and area efficiency and rail-to-rail input swings, the SAR architecture has become one of the more popular topologies.

Recent SAR designs have demonstrated outstanding bandwidth (running at hundreds of MS/s to GS/s range) and superior energy efficiency (with FoM 100fJ/conv.-step), but the resolution is limited to less than 10b ENOB. While scaling benefits speed and power efficiency, it does not improve capacitor matching, and the reduced supply headroom makes designing high-resolution ADC more difficult. Moreover, reference voltage settling also places a stringent settling requirement that limits the maximum operating speed. This work introduces redundancy and calibration into the design to help alleviate the settling and the mismatch problems. A sub-radix-2 SAR ADC is presented here with several new contributions. First, we incorporate the tri-level based switching[1]

into a new split-capacitor architecture to achieve higher energy efficiency. Second, we introduce a new method to implement redundancy directly into SAR with symmetric error-tolerance windows without the complexity and area overhead in[2]. Third, we develop a new code-density based background calibration algorithm for this architecture to calibrate against capacitor mismatches without requiring special calibration signals or additional analog hardware as in[3].

Our prototype is able to achieve a 67.4dB SNDR at 50MS/s while dissipating 2.1mW from a 1.2V supply, leading to a figure of merit (FoM) of 21.9fJ/conv.-step. Figure 1 shows the comparison with the state-of-the-art ADCs published in ISSCC and VLSI between 1997 and 2012. This ADC achieves the best FoM of any ADCs with greater than 10b ENOB and 10MS/s sampling rates.

- Y. Chen, S. Tsukamoto, and T. Kuroda, “A 9b 100MS/s 1.46mW SAR ADC in 65nm CMOS,” in IEEE Asian Solid-State Circuits Conference (A-SSCC), 2009, pp. 145-148. [↩]

- F. Kuttner, “A 1.2V 10b 20MSample/s Non-Binary Successive Approximation ADC in 0.13µm CMOS,” in IEEE International Solid-State Circuits Conference (ISSCC), 2002, pp. 176-177. [↩]

- W. Liu, P. Huang, and Y. Chiu, “A 12b 22.5/45MS/s 3.0mW 0.059mm CMOS SAR ADC Achieving over 90dB SFDR,” in IEEE International Solid-State Circuits Conference (ISSCC), 2010, pp. 380-381. [↩]