An Ultra-low-voltage Mixed-signal Front-end for a Wearable ECG Monitor

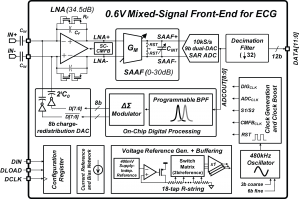

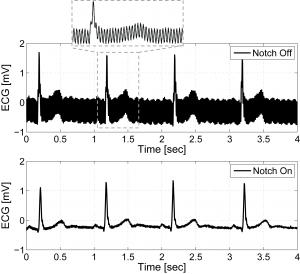

Circuits for wearable vital sign monitors have very stringent requirements on power dissipation due to limited energy storage capacity and the need for a long lifetime. Extending the time between battery recharge or replacement requires low-power electronics. We report a micro-watt mixed-signal front-end (MSFE) for ECG monitoring [1] that uses aggressive voltage scaling to maximize power-efficiency and ensure compatibility with low-voltage DSPs [2] . The MSFE shown in Figure 1 rejects 50/60Hz power-line interference (PLI) at the input of the system by using a mixed-signal feedback loop, enabling low-voltage operation by reducing dynamic range requirements. Analog circuits are optimized for ultra-low-voltage, and a SAR ADC with a dual-DAC architecture eliminates the need for a power-hungry ADC buffer. Oversampling and ΔΣ-modulation leveraging integrated digital processing are used to achieve ultra-low-power operation without sacrificing noise performance and dynamic range. Figure 2 shows ECG measurements on a male subject with the MSFE using gel electrodes and unshielded wiring. The PLI is clearly canceled when the PLI filter is enabled. The MSFE was prototyped in a 0.18µm CMOS process and consumes 2.9µW from 0.6V.

- Figure 1: System block diagram of the mixed-signal front-end for ECG monitoring including all voltage and current references, and clock generation.

- Figure 2: Measured ECG with the PLI notch filter disabled (top) and enabled (bottom).

- M. Yip, J. L. Bohorquez, and A. P. Chandrakasan, “A 0.6V 2.9µW mixed-signal front-end for ECG monitoring,” IEEE Symposium on VLSI Circuits, pp. 66-67, Honolulu, HI, Jun. 2012. [↩]

- J. Kwong and A. P. Chandrakasan, “An energy-efficient biomedical signal processing platform,” IEEE J. Solid-State Circuits, vol. 46, no. 7, pp. 1742-1753, Jul. 2011. [↩]