An On-Chip Test Circuit for Characterization of MEMS Resonator

- Category: Circuits & Systems, MEMS & BioMEMS

- Tags: dana weinstein, duane boning, john lee

Electromechanical resonators such as quartz crystals, surface acoustic wave (SAW) resonators, and ceramic resonators have become essential components in electronic systems. However, due to their large footprint and difficulty in integrating with CMOS processes, there has been much development in realizing microelectromechanical system (MEMS) resonators that achieve comparable performance yet have smaller footprint and are compatible with CMOS. As with other semiconductor devices, with increasing frequency and with decreasing device size into the submicron scale, variability has started to become a critical issue in MEMS resonators. However, one of the critical challenges is the lack of a characterization method that is accurate but efficient enough to be used for testing the large number of devices necessary to acquire accurate statistical distribution of the parameters of interest. This project proposes an on-chip test circuit that can accurately characterize a large number of resonators for variation analysis and that is general enough that it can be used with a wide range of resonators, not limited to specific frequencies or other properties. The proposed test circuit is based on a transient step response method using a voltage step that can accurately measure the resonant frequencies and the quality factor of devices [1] . The circuit employs a sub-sampling method to capture the high-frequency decay signal [2] and a simple analog-to-digital converter (ADC) [3] allowing complete digital interface, an important feature for test automation. SPICE level simulation combined with a behavioral simulation tool that was developed showed acceptable extraction errors of <1% for RS, <0.1% for Lx, <0.1% for Cx, <100 ppm for fs, and <1% for Qs. A test chip implementing the proposed test circuit has been designed and fabricated in NSC 0.18-um CMOS process.

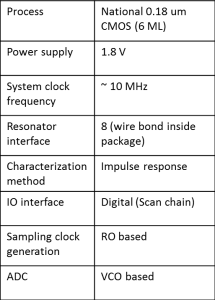

- Table 1: Detailed specification of the test chip.

- Figure 1: Die photo of the fabricated test chip.

- M. Zhang, N. Llaser, H. Mathias, and F. Rodes, “CMOS offset-free circuit for resonator quality factor measurement,” IEEE Electronic Letters, vol. 46, no. 10, p. 706, May 2010. [↩]

- R. Ho, B. Amrutur, K. Mai, B. Wilburn, T. Mori, and M. Horowitz, “Applications of on-chip samplers for test and measurement of integrated circuits,” in Proc. 1998 IEEE Symposium on VLSI Circuits, June, 1998, pp. 138-139. [↩]

- E. Alon, V. Stojanović, and M. A. Horowitz, “Circuits and techniques for high-resolution measurement of on-chip power supply noise,” IEEE Journal of Solid-State Circuits, vol. 40, no. 4, pp. 820-828, Apr. 2005. [↩]