Gate Recessed Technology for Normally-off GaN Transistors

- Category: Electronic Devices

- Tags: Bin Lu, Tomas Palacios

AlGaN/GaN high electron mobility transistors (HEMTs) have attracted a great interest for the next generation of power electronics due to their high electron mobility and high critical electric field. The standard AlGaN/GaN HEMTs are depletion-mode (D-mode) devices. However, enhancement-mode (E-mode) devices are highly desirable for power electronics as they can greatly simplify circuit designs and improve system reliability.

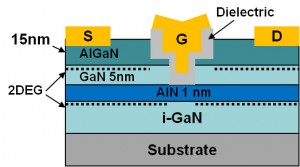

We have demonstrated a new AlGaN/GaN E-mode HEMT based on a dual-gate structure [1] . In this structure, the impact of the gate recess to the device on-resistance has been minimized by shrinking the recessed gate length. In the first version of the device, however, the channel electron mobility of the recess gate region was very poor, ~ 20 cm2/V.s. In order to improve the normally-off device channel mobility and uniformity of the threshold voltage, an improved device structure has been designed [2] . The new device structure is shown in Figure 1; it uses a GaN/AlN spacer between the AlGaN barrier and GaN channel in the conventional AlGaN/GaN HEMTs. The benefits of the GaN/AlN spacer structure are good channel transport property and high uniformity of threshold voltage. To fabricate E-mode devices, the AlGaN layer is removed from the gate region to deplete the channel. Then a selective etching between GaN and AlN can be used to stop the gate recess at the AlN layer, resulting in a uniform threshold voltage across the wafer. The AlN layer also prevents the gate dielectric from direct contacting the channel, reducing electron trapping and improving channel mobility.

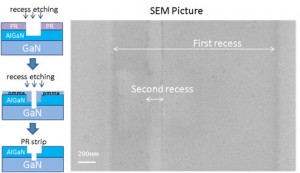

In order to fabricate the dual-gate transistor, a double gate recess must be used to prevent overheating of the photoresist during gate recess and improve the threshold voltage matching [1] in the dual-gate structure. The double-gate-recess process illustrated in Figure 2 allows a robust and flexible gate-recess technology for excellent normally-off operation.

- Figure 1: Schematic cross-section of E-mode GaN transistor using GaN/AlN spacer with dual-gate structure.

- Figure 2: Double gate recess process.