Fabrication of Si Nanowire-Based Capacitors for Power Management

- Category: Electronic Devices, Nanotechnology

- Tags: Carl Thompson

Capacitors have attracted considerable attention due to their potential as an energy buffer in a hybrid energy system. Improvement of the capacitor performance has been achieved by various approaches, one of which is introducing high surface-to-volume ratio structures to increase the effective electrode area. Therefore, fabrication of Si nanowire arrays and construction of capacitors based on these nanowires have been widely studied. Metal-catalyzed etching (MCE) is a new process to fabricate silicon nanowire arrays by the combination of film patterning techniques and the wet chemical etching step. The MCE technique is more appreciable than others because of its room temperature processing condition, which makes it compatible with current standard silicon integrated circuit fabrication technology. In this process, patterned metal films are used to catalyze the etching of silicon at the metal-silicon interface in a mixed etching of hydrofluoric acid and hydrogen peroxide.

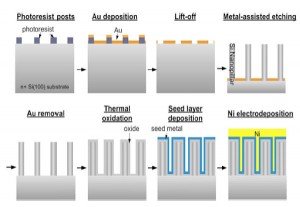

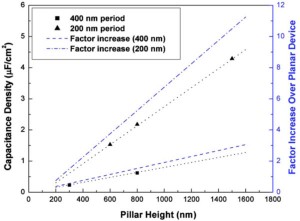

We have recently demonstrated the feasibility of using the MCE to fabricate Si nanowires to make nanocapacitors [1] . The fabrication process is described schematically in Figure 1. Interference lithography is used to make the anti-dot array pattern on the metal film, and the MCE process finally creates silicon wire arrays. Gold is then removed, and an oxide dielectric layer is grown in a tube furnace. Finally, electrodeposited nickel serves as the other electrode of the capacitor. We have demonstrated a factor of approximately 10 times improvement in the capacitance density over planar devices for nanocapacitors with a 200-nm period and 1.5-µm height. Figure 2 shows the results of capacitance measurements for different period and height pillar height capacitors. Further improvement of silicon nanowire capacitors can be achieved using wires with higher aspect ratios and smaller diameters and spacings.

- Figure 1: Schematic of the nanocapacitor arrays processing.

- Figure 2: Capacitance for different period and pillar height capacitors.

- S. W. Chang, J. Oh, S. T. Boles, and C. V. Thompson, “Fabrication of silicon nanopillar-based nanocapacitor arrays,” Applied Physics Letters, vol. 96, p. 153108, 2010. [↩]