Variation-aware Compact Model for Transistor and Interconnect

Continuous and aggressive scaling has led to increasing variation in process parameters, which are most critical in determining the quality and robustness of a device. These variations, such as threshold voltage, effective channel length, and mobility, interact with each other, resulting in drastic variance in circuit performance. Therefore there are emerging needs for characterizing, modeling, and predicting statistical trends with efficiency and accuracy.

For the characterizing level, we focus on exploring the variations of emerging devices or interconnects. We explore the impact of through-silicon vias (TSVs), which is a critical technology for future 3D integrated systems, on neighboring transistors. Though a few papers discuss the impact of TSVs on stress [1], a systematic test on TSVs’ impact on transistors’ performance is still needed. Our goal is to identify the accurate keep-out-zone distance, as well as how TSVs’ diameter, TSV-to-MOS spacing, and TSVs’ direction will affect neighboring transistors parameters such as mobility and sub-threshold leakage.

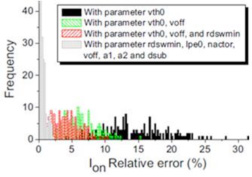

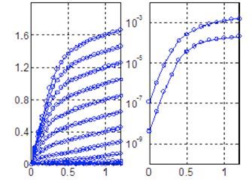

For the modeling level, we are trying to explore variability among compact modeling methods. We try to build a simple, physically based model that can capture sources of parameter variation. Khakifirooz has already built a semi-empirical transistor model with only 10 parameters, most by using direct measurement [2]. To capture the variability and for fast circuit simulations, this model should be improved for scalability and accuracy.

Based on the physically based, variation-aware compact model, efficient circuit analysis of process variation may be possible to achieve by linking with the Stochastic Dominant Singular Vectors (SDSV) Method [3], with less time and more efficiency than with the traditional Monte Carlo Method. While most prior works were based on algorithms in model-order reduction, our model captures basic semiconductor physics accurately and future optimization of it will be easy.

References

- A.P. Karmarkar, X. Xu and V. Moroz, ”Manufacturing, Reliability, and Performance Analysis of 3D Integration Structures Employing Through-Silicon Vias (TSVs),” 47th Annual International Reliability Physics Symposium, April 2009 [↩]

- A. Khakifirooz, O.M. Nayfeh and D. Antoniadis, “A Simple Semiempirical Short-Channel MOSFET Current–Voltage Model Continuous Across All Regions of Operation and Employing Only Physical Parameters,” IEEE TRANSACTIONS ON ELECTRON DEVICES, Vol. 56, No. 8, August 2009. [↩]

- T.A. El-Moselhy, “Field Solver Technologies for Variation-Aware Interconnect Extraction,” Ph. D. thesis, MIT, Cambridge, Feb. 2010. [↩]