SSTA Design Methodology for Low Voltage Operation

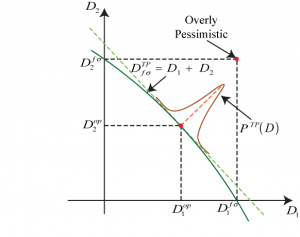

Figure 1: Joint PDF of stage delays in the TP has sharp maxima in the D-space. The point of maxima is called the operating point. Non-linear delay curve can be linearized about the operating point and the TP delay can be given as a linear combination of individual stage delays at the operating point

Statistical process variations have long been an important design issue. But until recently, process variations have been global process variations [1]. With transistor geometries shrinking below 65nm, however, a new kind of statistical variation, known as Local or Intra-die variation [2] has become important for logic.

In order to predict the statistical impact of local variations on circuit performance, it necessary to develop the statistical models that accurately reflect local variations and to develop a computationally efficient algorithm for performing SSTA using these models. This work develops an SSTA design methodology for low voltage operation. The approach is called Non-Linear Operating Point Analysis for Local Variations (NLOPALV) [3]. It addresses different aspects of timing analysis starting from standard cell library characterization to full-chip timing closure.

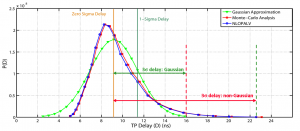

Figure 2: TP delay PDF is highly non-Gaussian at low-voltages with 3-sigma stochastic delay comparable to or more than the nominal delay. The zero-sigma delay is the nominal delay. TP delay PDF peaks at a point less than the nominal delay. Gaussian approximation gives highly optimistic estimate of the 3-sigma TP delay.

The goal of timing path (TP) analysis is to determine f-sigma stochastic delay. Computational efficiency of the NLOPALV approach comes from the concept of operating point, which allows us to determine the f-sigma TP delay without computing the entire delay PDF. Once the operating point is determined, the f-sigma TP delay can be computed as a linear sum of individual stage delays computed at the operating point (Figure 1). The NLOPALV approach is integrated with commercial CAD flow and validated on a digital signal processor implemented using commercial 28nm CMOS technology (Figure 2).

Any practical IC has millions of timing paths. In order to complete the timing analysis in an acceptable run-time, it is essential to reduce the number of paths that need to be analyzed. An approach to reduce the number of critical paths in a design has been developed using the concepts of NLOPALV. This approach can eliminate more than 95% of the paths in a very short run-time. The detailed NLOPALV analysis is then performed on the remaining paths to achieve timing closure for the IC.

References

- A. Agarwal, D. Blaauw and V. Zolotov, “Statistical timing analysis for intra-die process variations with spatial correlations,” Computer Aided Design 2003, ICCAD-2003, International Conference on, pp. 900-907, 2003. [↩]

- S. Sundareswaran., J. A. Abraham, A. Ardelea, R. Panda, “Characterization of Standard Cells for Intra-Cell Mismatch Variations”, Proceedings of the 9th international Symposium on Quality Electronic Design. March 17 – 19, 2008. [↩]

- R. Rithe, J. Gu, A. Wang, S. Datla, G. Gammie, D. Buss, A. Chandrakasan, “Non-linear operating point statistical analysis for local variations in logic timing at low voltage,” Proceedings of Design Automation and Test in Europe, pp. 965-968, March 2010. [↩]