SRAM Voltage-scaling in Advanced CMOS for Low Power

There is a need for large embedded memory that operates over a wide range of supply voltage compatible with the limits of static CMOS that also minimizes active and standby power. The technical challenge lies at the intersection of low-voltage operation and process variation. This work develops both statistical methods to efficiently design static random access memory (SRAM) and test chip prototypes.

A simulation methodology incorporating new techniques, known as “loop flattening” and “spherical sampling,” demonstrates the capability to evaluate SRAM read-access yield with speedups of 650x more [1]. It overcomes key challenges related to both the complex interconnections in the read path and conducting Importance Sampling simulation in a high-dimensionality parameter space (Figure 1).

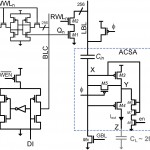

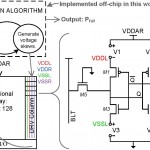

Additionally, an 8T SRAM fabricated in 45nm SOI CMOS exhibits voltage scalable operation from 1.2V down to 0.57V with access times from 400ps to 3.4ns [2]. Timing variation and the challenge of low-voltage operation are addressed with an AC-coupled sense amplifier (ACSA) (Figure 2). An area-efficient data path is achieved with a regenerative global bitline scheme. Finally, a data-retention voltage sensor has been developed to predict the mismatch-limited minimum standby voltage without corrupting the content of the memory (Figure 3).

- Figure 1: Illustration of Spherical Importance Sampling

- Figure 2: Column path of 8T SRAM with the ACSA.

- Figure 3: DRV Sensor Cell.

References

- M. Qazi, M. Tikekar, L. Dolecek, D. Shah, A. Chandrakasan, “Loop Flattening & Spherical Sampling: Highly Efficient Model Reduction Techniques for SRAM Yield Analysis,” Design, Automation and Test in Europe (DATE), pp. 801-806, March 2010. [↩]

- M. Qazi, K. Stawiasz, L. Chang, A. Chandrakasan, “A 512kb 8T SRAM Macro Operating Down to 0.57V with An AC-Coupled Sense Amplifier and Embedded Data-Retention-Voltage Sensor in 45nm SOI CMOS,” IEEE International Solid-State Circuits Conference (ISSCC), pp. 350-351, February 2010. [↩]