Low-Swing Token Flow Control Network-on-Chip Prototype

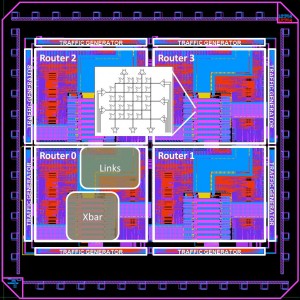

Figure 1: SWIFT Network-on-Chip with 4 routers connected in a 2x2 mesh. Traffic Generators allow varying activity at all ports to aid power measurements.

With the advent of chip multi-processors (CMPs), on-chip networks are critical for providing low-power communications that scale to high core counts. Recent Network-on-Chip (NoC) prototypes [1] [2] [3] have adopted mesh topologies with routers at intersections to manage the flow of packets across shared links. These routers consist of buffers, a crossbar switch, and allocators. The network primarily consists of two parts: a) the control path, which manages the router buffers to obtain maximum link utilization and avoid collisions, and b) the data path, which deals with the actual transmission of the data bits through the router switches and links.

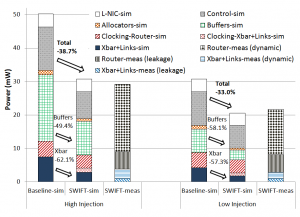

Figure 2: Power profile of each router in the SWIFT NoC compared with a baseline NoC router. SWIFT enables 38% power savings at high loads.

In this work, we reduced overall NoC power by tackling the power consumption in both these parts. We leveraged an architectural technique called Token Flow Control (TFC) [4] which creates dynamic fast-paths in the network by acquiring and chaining together “tokens”, which are hints about occupancy at router buffers. This enables packets to dynamically bypass buffering at intermediate routers, thereby reducing both latency, and the power of the control path. The proposed router is able to sustain the same saturation throughput as a baseline [2], [3] with 39% lower latency, and 49% lower buffer power. Along the data path, we designed and integrated a custom low-swing crossbar and low-swing core-core 64-bit links. The crossbar in our design is tiled linearly across, as opposed to the traditional diagonal-style switch, and also supports clock gating. The low-swing crossbars and links lower the transmission power 62%.

We call our design the SWIFT NoC (SWing-reduced Interconnect For a Token-based Network-on-Chip). Figure 1 shows an experimental prototype comprising 4 routers. It operates at 400 MHz (limited by IR drop) and verifies the advantages of our approach. Figure 2 highlights the power breakdown of various components of the SWIFT router and a baseline router. We observe an overall power savings of 38%.

References

- M. B. Taylor, et al., “The Raw microprocessor: A computational fabric for software circuits and general-purpose programs,” IEEE Micro, vol. 22, no. 2, pp. 25–35, Mar.-Apr. 2002. [↩]

- K. Sankaralingam, et al., “Exploiting ILP, TLP, and DLP with the polymorphous TRIPS architecture,” in Proc. International Symposium on Computer Architecture, pp. 422–433, Jun. 2003 [↩] [↩]

- S. Vangal, et al., “An 80-Tile 1.28TFLOPS Network-on-Chip in 65nm CMOS,” in IEEE International Solid State Circuits Conference, Digest of Technical Papers 2007, pp. 98-589, Feb. 2007. [↩] [↩]

- A. Kumar, et al., “Token Flow Control” in Proc. 41st International Symposium on Microarchitecture, pp. 342-353, Nov. 2008. [↩]