FastCaplet: An Efficient 3-D Capacitance Extraction Solver for VLSI Interconnects Using Instantiable Basis Functions

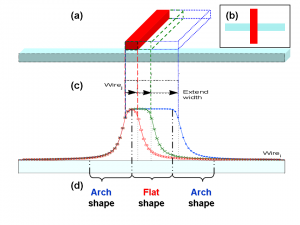

Figure 1: (a) The 3D view of a pair of crossing wires. The upper wire is stretched out to three different widths. (b) The top view of the geometry (c) The front view of the lower wire and the charge distribution induced by the upper wire of three different widths (d) The definition of arch and flat shapes extracted from the distribution induced by the widest upper wire. Those shapes are reusable in other VLSI geometries.

State-of-the-art capacitance extraction methods for Integrated Circuits (IC) involve scanning 2-D cross sections and interpolating 2-D capacitance values using a table-lookup approach. This approach is fast and accurate for a large percentage of IC wires. It is, however, quite inaccurate for full 3-D structures, such as comb capacitors or crossing wires in adjacent metal layers. These cases require electrostatic field solvers. Unfortunately, standard field solvers are inherently very time-consuming, making them completely impractical in typical IC design flows. Even fast matrix-vector product approaches (e.g., fast-multipole [1] or pre-corrected FFT [2] ) have a significant computational overhead and start to scale linearly with the number of conductors only when there are more than several hundred wires. In this project we are developing a new 3-D extraction field solver that is extremely efficient, especially for the smaller scale extraction problems: the full 3-D structures comprising ten to one hundred conductors that cannot be handled by the 2-D scanning and table-lookup approach.

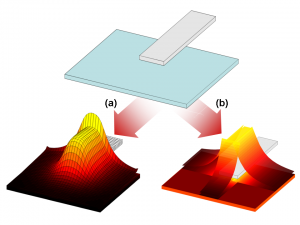

Figure 2: Partially overlapping wires are extracted by (a) traditional boundary element methods with piecewise constant basis functions, using 572 unknowns, and by (b) Fast-Caplet with the instantiable basis functions, using only 17 unknowns. It takes 760 ms and 30 ms to extract for each method, respectively.

Because of the highly restrictive design rules of today’s sub-micro to nano-scale IC technologies, template charge distributions extracted from simple model structures can be reused to instantiate (stretch and combine) basis functions in other realistic complicated geometries, such as wire buses and metal capacitors. This “template-instantiation” strategy largely reduces the number of unknowns and computation time without additional overhead as in [3], [4]. This work verifies that only two fundamental templates, shown in Figure 1, are required for virtually all valid IC geometries [5]. Also, this work shows that when considering practical aspect ratios and wire spacing, the edge and corner charge singularities [6] can be totally neglected for a target 5% error in capacitance. In the example in Figure 2, a preliminary MATLAB version of our algorithm runs 25 times faster and requires 33 times fewer unknowns compared to using standard piecewise constant basis functions.

References

- K. Nabors and J. White, “Fast-Cap: A Multipole-Accelerated 3-D Capacitance Extraction Program,” IEEE Transactions on Computer-Aided Design, vol.10, no. 10, pp. 1447-1459, November 1991. [↩]

- J.R. Phillips and J.K. White, “A Precorrected-FFT method for Electrostatic Analysis of Complicated 3-D Structures,” IEEE Trans. on Computer-Aided Design, vol. 16, no.10, pp. 059-1072, October 1997. [↩]

- K. Nabors and J. White, “Fast-Cap: A Multipole-Accelerated 3-D Capacitance Extraction Program,” IEEE Transactions on Computer-Aided Design, vol.10, no. 10, pp. 1447-1459, November 1991. [↩]

- J.R. Phillips and J.K. White, “A Precorrected-FFT method for Electrostatic Analysis of Complicated 3-D Structures,” IEEE Trans. on Computer-Aided Design, vol. 16, no.10, pp. 059-1072, October 1997. [↩]

- Y-C. Hsiao, T. El-Moselhy, L. Daniel, “Efficient Capacitance Solver for 3D Interconnect Based on Template-Instantiated Basis Functions,” Proceedings of the 18th Conference on Electrical Performance of Electronic Packaging and Systems, pp. 179-182, Portland, Oregon, 2009. [↩]

- Y. Zhang, A. H. Zemanian, “Contributions of corner singularities of the capacitances of interconnections wires,” IEEE International Symposium on Circuits and Systems, 1995 [↩]