Design and Demonstration of Integrated Micro-electro-mechanical (MEM) Relay Circuits for VLSI Applications

Silicon CMOS circuits have a well-defined lower limit on their achievable energy efficiency due to subthreshold leakage. Once this limit is reached, power constrained applications will face a cap on their maximum throughput independent of their level of parallelism. Avoiding this roadblock requires an alternate device with steeper sub-threshold slope – i.e., lower VDD/Ion for the same Ion/Ioff ((H. Kam, et al., “Circuit Level Requirements for MOSFET Replacement Devices,” in IEDM Tech. Dig., 2008, pp. 427.)). One promising class of such devices is electro-statically actuated micro-electro-mechanical (MEM) relays with nearly ideal Ion/Ioff characteristics. Although mechanical movement makes MEM relays significantly slower than CMOS, they can be useful for a wide range of VLSI applications by reexamining traditional system- and circuit-level design techniques to take advantage of the electrical properties of the device. Unlike in CMOS circuit design, logic functions in MEMS circuit design should be implemented as a single complex gate with minimum-sized relays, resulting in significantly reduced logic complexity. We have recently shown that with optimized circuit topologies MEM relays may potentially enable ~10x lower energy over CMOS at up to ~0.1-1GHz frequencies [1]. This work takes initial steps towards experimental validation of these principles by leveraging recently developed relay technology and reliability enhancements [2] [3] to demonstrate several monolithically integrated MEM relay-based building blocks. Specifically, our chip includes logic, memory, I/O, and clocking structures, and we demonstrate successful basic functionality and circuit composition [4]. These relay circuits illustrate a range of important functions necessary for the implementation of integrated VLSI systems, and give insight into circuit design techniques that leverage the physical properties of these devices.

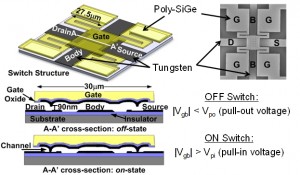

- Figure 1: SEM, diagram, and operating states of the MEM relay device.

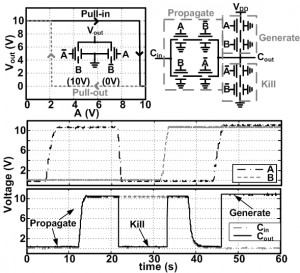

- Figure 2: Schematic and measured VTC/transient waveforms for a MEM-relay based inverter/XOR and carry generation circuit.

References

- F. Chen, et al., “Integrated Circuit Design with NEM Relays,” in IEEE/ACM International Conference on Computer Aided Design (ICCAD), pp. 750-757, 2008. [↩]

- R. Nathanael, et al., “4-Terminal Relay Technology for Complementary Logic,” in IEDM Tech. Dig., 2009, pp. 223-226. [↩]

- H. Kam, et al, “Design and Reliability of a Micro-Relay Technology for Zero-Standby-Power Digital Logic Applications,” in IEDM Tech. Dig., 2009, pp. 809–812. [↩]

- F. Chen, et al., “Demonstration of Integrated Micro-Electro-Mechanical Switch Circuits for VLSI Applications,” in International Solid-State Circuits Conference (ISSCC Tech. Dig.), pp.150-151, 7-11 Feb. 2010. [↩]