A Quad Full HD Low-power H.264/VC-1 Single-chip Encoder

The commercialization of numerous high-performance multimedia devices, in particular portable devices such as camera phones, high-resolution video camcorders, and digital still-cameras, has resulted in an increased demand for more power-efficient system designs. As resolutions for video capture and playback scale beyond high definition, more aggressive low-power circuit design techniques are needed to prolong the battery life [1] . Reconfigurable architectures are also required to support multiple video formats.

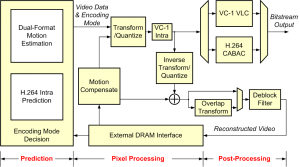

This work explores algorithmic, architectural, and circuit-level innovations that can be applied to each of the functional blocks in a multi-standard video encoder to enable low-voltage operation while maintaining performance. All functional blocks process the video data in a frame-parallel and macro-block parallel manner to reuse the intermediate data among different frames/macroblocks. All on-chip SRAMs are designed specifically for low-voltage operation. The motion estimation unit employs a predictor-based motion searching scheme and an early-rejection algorithm to reduce the redundant computation. The transforms and intra-prediction blocks exploit data-dependency and matrix factorization to enable re-configurability and lower power. The entropy encoder block utilizes the available data to perform parallel encoding with partitioned look-up tables to reduce the energy consumption.

A reconfigurable video encoder supporting both the H.264/AVC High Profile Level 5.1 [2] and VC-1 Advanced Profile Level 4.0 [3] video coding standards is being implemented on a single low-power ASIC. This encoder is designed to process video sequences with Quad Full HD (4Kx2K pixels per frame) resolution at 30 frames per second with a 0.5V power supply voltage. The estimated power consumption is 10 times lower than the state-of-the-art video encoder ASICs [4] .

References

- Finchelstein, D. F., V. Sze, M. E. Sinangil, Y. Koken, and A. P. Chandrakasan, “A Low-Power 0.7-V H.264 720p Video Decoder,” IEEE Asian Solid-State Circuits Conference, pp. 173-176, November 2008. [↩]

- “Advanced Video Coding for Generic Audiovisual Services,” ITU-T H.264, March 2009. [↩]

- “VC-1 Compressed Video Bitstream Format and Decoding Process,” SMPTE 421M-2006, February 2006. [↩]

- L.-F. Ding, et al., “A 212MPixels/s 4096×2160p multiview video encoder chip for 3D/quad HDTV applications,” 2009 ISSCC Digest of Technical Papers, pp. 154-155, February 2009. [↩]