A Low-voltage Zero-crossing-based Delta-Sigma ADC

Many analog signal processing circuits use operational amplifiers (opamps) in a negative feedback topology. Error in these feedback systems is inversely proportional to the gain of the opamp. Because scaled CMOS technologies use shorter channel lengths and require lower power supply voltages, it becomes more difficult to implement high gain opamps. Recently, techniques were proposed that use a comparator [1] , or more generally, a zero-crossing detector [2] , rather than an opamp to implement switched-capacitor topologies.

In this project, we investigate very-low-voltage delta-sigma converters. One of the biggest challenges of low-voltage circuits is the transmission gates that must pass the signal. If the signal is near the middle of the power supply range, neither the NMOS nor the PMOS transistor has sufficient gate drive to pass the signal properly. The switched-opamp technique [3] was proposed to mitigate this problem. In this technique, the output of the opamp is directly connected to the next sampling capacitor without a transmission gate to perform charge transfer. During the charge-transfer phase, the opamp is switched off, and the output is grounded.

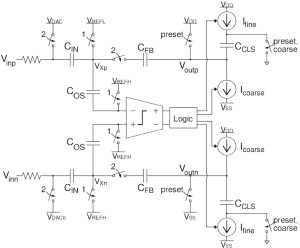

Much like standard switched-capacitor circuits, zero-crossing-based (ZCB) circuits use two-phase clocking, having both sampling and charge-transfer clock phases. Unlike standard switched-capacitor circuits, in a ZCB circuit all current sources connected to the output node are off at the end of the charge-transfer phase. Therefore, there is no opamp or current source to turn off to accommodate the charge transfer without a transmission gate. Thus, the ZCB technique is inherently better suited to low-voltage applications than switched-opamp circuit topologies. Figure 1 shows a fully-differential low-voltage ZCB integrator stage using the combined techniques. New output pre-sampling and voltage ramp linearization techniques were used. We have designed and tested a fourth-order delta-sigma ADC that uses this integrator stage for audio-band applications. The prototype ADC achieves 73 dB SNDR for 60-kHz input bandwidth while dissipating 1.2 mW power from a 1-V supply.

References

- T. Sepke, J.K Fiorenza, C.G. Sodini, P. Holloway, and H.-S. Lee, “Comparator-based switched-capacitor circuits for scaled CMOS technologies,” 2006 IEEE ISSCC Digest of Technical Papers, Feb. 2006, p. 220. [↩]

- L. Brooks, and H.-S. Lee, “A 12b, 50 MS/s, fully differential zero-crossing-based pipelined ADC,” 2009 IEEE ISSCC Digest of Technical Papers, Feb. 2007, pp.460-461. [↩]

- J. Crols and M. Steyaert, “Switched-opamp: an approach to realize full CMOS switched-capacitor circuits at very low power supply voltages,” IEEE Journal of Solid-State Circuits, vol. 29, no. 8, pp. 936-942, Aug. 1994. [↩]