A Compressed Sensing Acquisition System for Wireless and Implantable Sensors

In wireless sensor applications such as implantable neural recording arrays, the high energy cost to transmit a bit of information and the radio’s limited bandwidth necessitate data compression or filtering at the sensor to limit energy consumption and data throughput [1]. Many bio-signals of interest occur infrequently, so transmitting data only when a significant event is detected can be effective in reducing data and power [2]. Existing data compression strategies for biophysical monitoring adopt this approach and rely on known signal characteristics in order to detect significant events [1] [2] [3] [4] [5]. However, the filtered data contains limited information. In neural recorders, the data is often limited to just the time and amplitude of a neural spike event rather than the signal itself [1] [3]. Meanwhile, feature extraction approaches require training, are usually signal-specific, and still do not provide the original signal [4] [5].

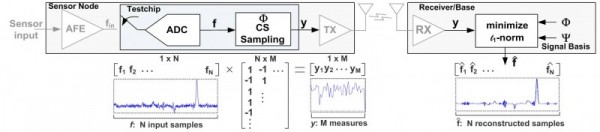

In this work, we present the design and implementation of a new sensor-system architecture (Figure 1) based on the theory of compressed sensing (CS) [6] that addresses both the energy and telemetry bandwidth constraints of wireless sensors. This approach reduces the average radio power by exploiting signal sparseness to encode the data at a high compression factor (~40x) while enabling a faithful reconstruction of the entire original signal. The reconstruction process also enables power reduction in the frontend circuitry by relaxing the noise and resolution requirements of the AFE and ADC by nearly an order of magnitude. An efficient implementation of the CS sampling is realized in a 90-nm CMOS process and consumes 1.9µW at 0.6V and 20kS/s.

Figure 1: Block diagram of the proposed sensor system architecture showing the equivalent mathematical function of the CS sampling matrix.

References

- R. Harrison, et al., “A low-power integrated circuit for a wireless 100-electrode neural recording system,” IEEE Journal of Solid-State Circuits, vol. 42, pp. 123-133, 2007. [↩] [↩] [↩]

- B. Gosselin and M. Sawan, “Circuits techniques and microsystems assembly for intracortical multichannel ENG recording,” IEEE Custom Integrated Circuits Conference, pp. 97-104, 2009. [↩] [↩]

- R. Olsson and K. Wise, “A three-dimensional neural recording microsystem with implantable data compression circuitry,” IEEE Journal of Solid-State Circuits, vol. 40, pp. 2796-2804, 2005. [↩] [↩]

- N. Verma, et al., “A Micro-Power EEG Acquisition SoC With Integrated Feature Extraction Processor for a Chronic Seizure Detection System,” IEEE Journal of Solid-State Circuits, vol. 45, pp. 804-816, 2010. [↩] [↩]

- V. Karkare, et al., “A 130-µW, 64-Channel Spike-Sorting DSP Chip,” IEEE Asian Solid-State Circuits Conference, vol. 1, pp. 289-292, 2009. [↩] [↩]

- D. Donoho, “Compressed sensing,” IEEE Transactions on Information Theory, vol. 52, 2006, pp. 1289–1306. [↩]