A 6.25-Gb/s Adaptive Fractionally Spaced Receive Equalizer with Voltage-time Conversion

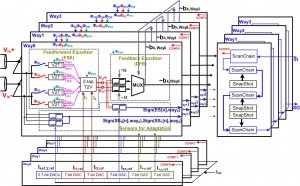

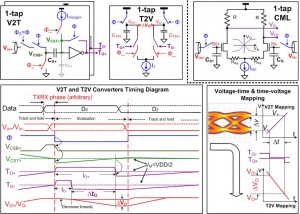

This work describes an architecture and circuit implementation of a fractionally spaced equalizer (FSE) receiver [1], built to unify equalization and phase synchronization in high-speed links, as shown in Figure 1. To achieve the desired linearity for adaptation with good energy efficiency, large input dynamic range, and high operation rate, the FSE is designed using a voltage-time conversion technique [2]. The proposed auto-zero inverter-based threshold detectors are able to compensate for the detection threshold mismatch while converting voltage signals to timing signals, a trait missing in [1]. A two-tap quad-rate FSE receiver with one-tap DFE is fabricated in 90-nm bulk CMOS technology, occupying a 0.03 mm2 active area. With a 1.2-V supply, it achieves a 6.25-Gbps rate, 3.6-pJ/bit efficiency and 5 effective bits of linearity.

A modified sign-sign LMS adaptive algorithm is used to tune the FSE tap weights to mitigate the inter-symbol interference (ISI) for the arbitrary receiver phase. Based on data conditioning, it reduces the quantization noise and overcomes divergence issues of the traditional FSE sign-sign LMS algorithm.

-

Figure 1: Architecture of the 4-way interleaved 2-tap FSE and 1-tap DFE receiver with on-chip adaptation sensors. Scan-chain and snapshot are applied for in-situ link characterization and the off-chip adaption experiment.

- Figure 2: FIR tap implementation concept with CML and V2T technique. For CML implementation, the transconductance of the input devices determines the linearity, while for the V2T implementation, the charge current Icharge+/- determines the linearity.

References

- S. Song, B. Kim, and V. Stojanović, “A Fractionally Spaced Linear Received Equalizer with Voltage-to-Time Conversion,” IEEE Symposium on VLSI Circuits Dig. Tech. Papers, June 2009. [↩] [↩]

- L. Brooks and H.-S. Lee, ” A Zero-Crossing-Based 8-bit 200 MS/s Pipelined ADC,” IEEE Journal of Solid-State Circuits, Dec. 2007. [↩]