Project title: InGaAs HEMTs: a beyond-the-roadmap logic technology? Kim, D. H. and J. A. del Alamo, "Beyond CMOS: Logic Suitability of In_0.7 Ga_0.3 As HEMT." To be presented at 2006 International Conference on Compound Semiconductor Manufacturing Technology (CS MANTECH), Vancouver, BC (Canada), April 24-27, 2006.

Kim, D.-H., J. A. del Alamo, J. H. Lee, and K. S. Seo, "Performance Evaluation of 50 nm In_0.7 Ga_0.3 As HEMTs for Beyond-CMOS Logic Applications." 2005 IEEE International Electron Devices Meeting, Washington, DC, December 5-7, 2005, pp. 787-790.

Staff: Dr. Dae-Hyun Kim (Postdoctoral Fellow), Niamh Waldron (Intel Foundation Ph.D. Fellow)

Sponsor: Army Research Laboratory, Intel, MARCO-MSD

Description:

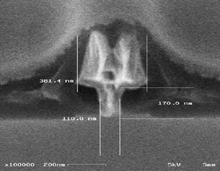

With the end of the CMOS roadmap looming, identifying a new logic device technology is becoming increasingly pressing. For the last 20 years, InAlAs/InGaAs HEMTs have held the world record of frequency response. This technology is space qualified and it is also a leading candidate for 160 Gb/s optical fiber systems. Until recently, there has not been an analysis of the suitability of InGaAs HEMTs for logic applications. Figures of merit relevant to logic, such as CV/I (gate delay), ION/IOFF, DIBL and subthreshold slope, have not been evaluated in this family of devices. At MIT, we have fabricated 100 nm InAlAs/InGaAs HEMTs and we have found that they offer excellent logic performance. However, at 100 nm gate lengths, these devices have already reached their scaling limit. Further gate length scaling will require aggressive insulator thickness scaling.

Publications:

Kim, D.-H., J. A. del Alamo, J. H. Lee, and K. S. Seo, "The Impact of Side-Recess Spacing on the Logic Performance of 50 nm In_0.7 Ga_0.3 As HEMTs." To be presented at 2006 Indium Phosphide & Related Materials Conference (IPRM), Princeton, NJ, May 8-11, 2006.