Very-high-speed Serial Links

- Category: Circuits & Systems

- Tags: amr suleiman, vladimir stojanovic

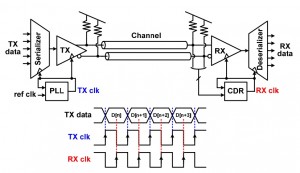

Demand for bandwidth in chip-to-chip communication has been increasing as the industry demands a higher quantity and quality of information. Serial links are a suitable architecture for this kind of transmission because of speed, power, and area limitations on parallel links. Figure 1 shows an example of basic serial link components. This research focuses on the design of a power-efficient transmitter and receiver circuits for backplane serial links targeting link speeds of hundreds of Gb/s in the specifications for the next generation of links.

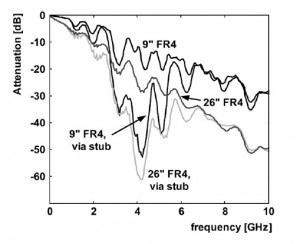

Several challenges face such high speeds. Link rates are increasing to the point where they are running into the bandwidth limitation of the cables or backplanes. This bandwidth limitation is caused by dielectric loss, skin-effect, and impedance discontinuities [1] . Additionally, in many applications the wires within a system can have significantly different channel characteristics, as shown in Figure 2. Different equalization techniques are used to compensate for channel response and achieve a bigger eye at the receiver [2] . Clocking in both the transmitter and receiver is another problem, with low supply voltages and low power requirements. Transmitter and receiver must be synchronous, to correctly sample the received data at the maximum eye opening. Besides, targeting such speeds pushes current CMOS technologies to their limits. As a result, new ideas and circuit tricks are desired.

This research concentrates on the transmitter side. Work is now being done on a new transmitter equalizer technique, which introduces about double the eye opening of conventional FIR feed-forward equalizers. A behavioral model for the whole serial link system was developed last year, and more work is being dedicated to improving its accuracy and accounting for different transistor technologies and circuit architectures. The project is done in collaboration with UC Berkeley, UCLA, and OSU.

- Figure 1: Basic link components: the transmitter, the channel, and the receiver.

- Figure 2: Frequency response of different channels within the same backplane: FR4 material, 9 and 26 trace length, top and bottom routing layers.

- S. V. Stojanović, A. Ho, B. W. Garlepp, F. Chen, J. Wei, G. Tsang, E. Alon, R. T. Kollipara, C. W. Werner, J. L. Zerbe, and M. A. Horowitz, “Autonomous dual-mode (PAM2/4) serial link transceiver with adaptive equalization and data recovery,” IEEE Journal of Solid-State Circuits, vol. 40, no. 4, pp. 1012-1026, Apr. 2005. [↩]

- R. Sredojević and V. Stojanović, “Fully digital transmit equalizer with dynamic impedance modulation,” IEEE Journal of Solid-State Circuits, vol. 46, no. 8, pp. 1857-1869, Aug. 2011. [↩]