- Authors: Y.-C. Hsiao, A. Megretski, L. Daniel, Y.-C. Hsiao, A. Megretski, L. Daniel

During recent years, researchers in the Electronic Design Automation community have made great efforts to develop new techniques to automatically generate accurate compact models of “nonlinear”system blocks. The majority of the existing methods for creating stable reduced models of nonlinear systems, such as [] , require knowledge of the internal structure of the system, as well as access to the exact model formulation for the original system. Unfortunately, this information may not be easily available if a designer is using a commercial design tool or may not even exist if the system to be modeled is a physical fabricated device.

As an alternative approach to the standard nonlinear model reduction, we propose a system-identification procedure. This procedure requires only data available from simulation or measurement of the original system, such as input-output training data pairs. However, simply fitting an arbitrary nonlinear model to the training data does not guarantee that the solution is a valid dynamic model. A valid dynamic model must be stable when evaluated in a time domain simulator. The challenge is to search for a nonlinear dynamic model that simultaneously satisfies the stability requirement and optimally matches the training data. We have managed to formulate such problem as a semi-definite convex optimization problem. The proposed optimization formulation, explained in detail in [] as an efficient extension of [] , allows us to specify completely the complexity of the identified reduced model through the choice of both model order and nonlinear function complexity.

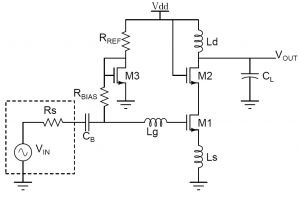

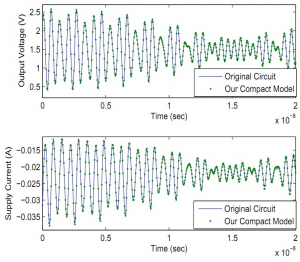

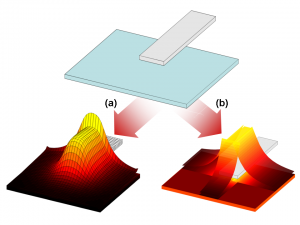

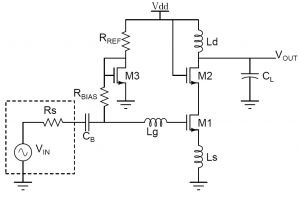

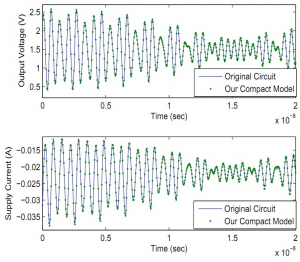

Applications for the proposed modeling technique include analog circuit building blocks such as operational amplifiers and power amplifiers, and individual circuit elements such as transistors. The resulting compact models may then be used in a higher-level design optimization process of a larger system. One such example of an analog circuit block is the low-noise amplifier shown in Figure 1; it contains both nonlinear and parasitic elements. For this example, input-output training data was generated from a commercial circuit-simulator and used to identify a compact nonlinear model. Figure 2 compares the output responses of the original system and the identified model.

-

-

Figure 1: Application example: Low-noise amplifier designed in CMOS technology.

-

-

Figure 2: Time domain outputs, over a small portion of the period, of the original LNA circuit from a commercial circuit simulator (solid line) and the stable nonlinear compact model identified by our procedure (dots) in response to an input signal different from the training signals.

- Authors: Y.-C. Hsiao, P. Triverio, T. Moselhy, J. White, L. Daniel

- Sponsorship: MIT-SkTech

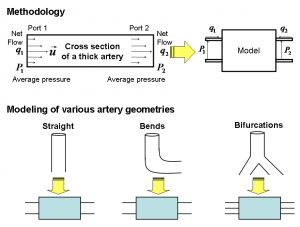

Understanding certain medical conditions requires understanding specific aspects of the arterial blood flow. For instance, diagnosing atherosclerosis requires capturing detailed flow inside an arterial segment. Such study requires developing accurate solvers for the detailed equations describing both the blood flow and the elastic behavior of the arteries. At the other end of the spectrum, studying hypertension requires computing pressure and averaged flow over a larger arterial network. Such analysis requires developing compact computationally inexpensive models of complex segments of the arterial network. These models relate the pressure and average flow at the terminals of the arterial segments and must be easily interconnected to form complex and large arterial networks.

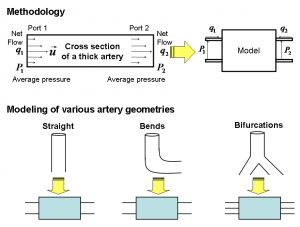

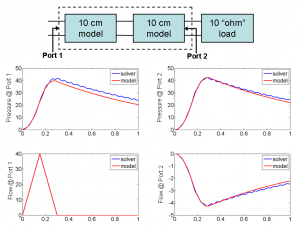

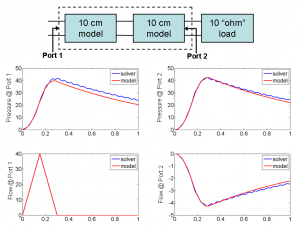

In this project we are developing a 2-D fluid-structure interaction solver to accurately simulate blood flow in arteries with bends and bifurcations. Such blood flow is mathematically modeled using the incompressible Navier-Stokes equations. The arterial wall is modeled using a linear elasticity model [] . Our solver is based on an enhanced immersed boundary method (IBM) [] . As a second step we are developing system identification techniques [] to generate passive models for complex arterial segments such as large arteries, arterial bends, and bifurcations. We have validated our solver results versus reference results obtained from MERCK Research Laboratories for a straight vessel of length 10 cm and diameter 2 cm. Our results for pressure, flow, and radius variations are within 3% of those obtained from MERCK. Furthermore, we are validating our model results by cascading different models and comparing the results of the resulting network to those predicted by our solver. Our preliminary results for pressure and flow at the terminals of the models are within 10% of those obtained from the full simulator. In addition, with our models we reduce the computational time by more than 100,000 times.

-

-

Figure 1: We use i) our immersed boundary method for incompressible Navier-Stokes to extract a complete model ii) our system identification technique to construct a reduced model [] . The lower part shows three major artery geometries we use for modeling a cardiovascular system.

-

-

Figure 2: A 20-cm artery is constructed by cascading two 10-cm artery models terminated with a matched load. The transient simulation results of the cascaded model are compared with those of a 20-cm artery solved by our immersed boundary method solver.

- Authors: Y.-C. Hsiao, L. Daniel

- Sponsorship: SRC/FCRP IFC, SRC/FCRP GRC, Mentor Graphics, AMD, Freescale

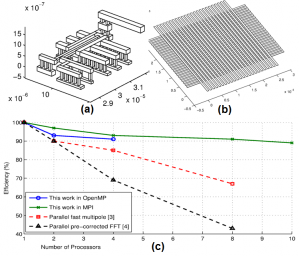

Traditional interconnect capacitance extraction tools usually employ 2D scanning and table look-up methods for fast extraction. For some structures, e.g., partially overlapping wires and comb capacitors, 2D scanning methods fail to generate accurate results (i.e. within 5% error), therefore using 3D field solvers becomes necessary despite the much slower performance. Accelerated field solvers have been proposed, such as FastCap [] and Precorrected FFT [] whose accelerations are effective only for large, semi-global structures of hundreds of wires. More importantly, [] and [] demonstrated that such two acceleration methods are not efficiently parallelizable, showing rapid degradation of parallel efficiency with the number of parallel nodes (40% to 60% at eight nodes).

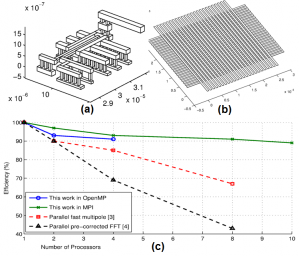

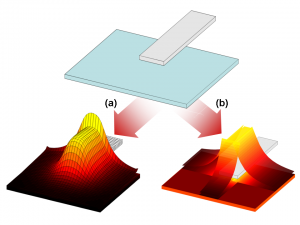

We propose an efficiently parallelizable acceleration method for local, small-to-medium structures of tens of wires, targeting errors within 5%. We adopt our instantiable basis functions [] as a compact charge distribution representation in the boundary element method. Our instantiable basis functions are usually 30 times more compact than traditional piecewise constant (PWC) basis functions [] [] [] [] in terms of required basis functions for the same capacitance accuracy (Figure 1). Such compactness not only accelerates the single-node execution (six times in Figure 2.a) but also greatly improves the parallel efficiency (Figure 2.b) by redistributing the computation between the hard parallelizable system solving part (from 90% of total execution to less than 5%) and the embarrassingly parallelizable matrix filling part (from 10% to more than 95%) [] . We will release the complete tool set, from input gds2 layout files to capacitance matrices, in the public domain.

-

-

Figure 1: Charge distribution solutions represented by (a) 572 PWC basis functions and (b) 17 instantiable basis functions, respectively. Capacitance errors for both cases are 2% w.r.t. a reference value extracted by the standard BEM with fine PWC discretization.

-

-

Figure 2: (a) Industrial example. The algorithm is 6x faster than FASTCAP [] for single-threaded execution at same accuracy (2.8% error w.r.t. a reference value). (b) 24×24 bus example. (c) Parallel efficiency vs. algorithms [] and [] .