Non-volatile Processing for Battery-less Operation

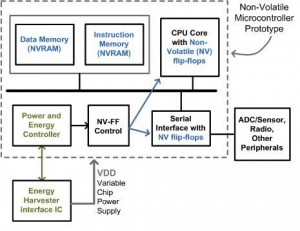

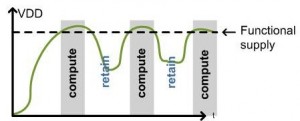

The emergence of faster and lower-power non-volatile memory technologies has opened up the investigation of ways to integrate these technologies into digital systems [1] . This work explores the implementation of a battery-less sensor node as a demonstration of a new kind of ultra-low-power system. In order to operate without a battery, the system must manage the state efficiently in terms of energy overhead during frequent and spontaneous periods of power loss. Figure 1 shows the system block diagram. The memory hierarchy from instruction and data memory to registers in the logic is implemented with non-volatile memory elements. As a result, during spontaneous power disruptions, the system quickly saves the state, and, during power recovery, the system quickly restores the state and resumes computation. In order to achieve the desired functionality (illustrated in Figure 2), a custom non-volatile register must be designed and integrated into a digital design flow. Furthermore, the power management unit must be augmented to interface with the energy harvester, the clocking, and registers in the digital circuitry.

- Figure 1: Block diagram of non-volatile processor for use in a battery-less sensor node.

- Figure 2: Time profile of unreliable power supply overlaid with intended behavior of the non-volatile processor.

- T. Kawahara, “Scalable spin-transfer torque RAM technology for normally-off computing,” IEEE Design & Test of Computers, vol. 28, no. 1, pp. 52-63, Jan.-Feb. 2011. [↩]