High-throughput Digital Baseband for mm-Wave Outphasing Power Amplifiers

- Category: Circuits & Systems

- Tags: vladimir stojanovic, zhipeng li

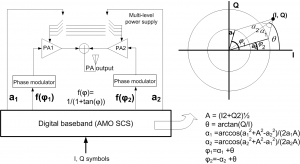

Outphasing power amplifier architectures such as linear amplification with nonlinear components (LINC) have been used to improve the power efficiency of higher-order modulation formats by utilizing more efficient, nonlinear power amplifiers (PA) [1] . The asymmetric multilevel outphasing (AMO) has been recently proposed to further improve the average power efficiency of traditional LINC PA by introducing multiple supply levels [2] . Figure 1 shows the overall AMO system architecture, where each transmitted sample is decomposed into two vector signals with different phases and restricted amplitude choices. Each decomposed vector signal is first modulated by the phase modulator. Then the high-efficiency switching PA amplifies the signal with appropriate amplitudes. Finally the two vectors are combined to deliver the final output. One bottleneck for both LINC and AMO architectures is the signal component separation (SCS) task, whose functionality is shown on the right side of Figure 1. SCS involves complex functional computations, such as square-root and trigonometric functions, which degrade the overall power-added efficiency, especially at high system throughputs and moderate output powers.

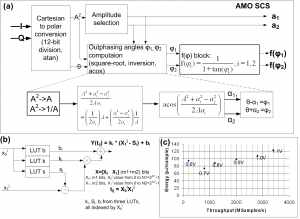

Traditional digital SCS implementations are usually based on look–up-table (LUT) designs [3] and are therefore limited by accuracy and area while their analog counterparts are usually limited by speed [4] . To overcome these limitations, we propose to simplify the function computations by using a piece-wise linear spline approximation for each function, as shown in Figure 2(b). With careful design of the constant and slope terms, each function computation only involves a small LUT, one multiplication, and two additions. This approach achieves a 6-10x energy efficiency improvement over the traditional CORDIC [5] for trigonometric functions and polynomial fittings. The overall SCS system’s micro-architecture is shown in Figure 2(a), where all the functional computations are implemented with our approximation approach. This system is fabricated in a 45-nm SOI process. The chip runs up to 1.7GHz (3.4 Gsamples/s) at 1.1V supply. Figure 2(c) shows the energy efficiency for different throughput. The minimum-energy point is 74pJ per sample at 800Msamples/s throughput.

- Figure 1: AMO system overview and the functionality of the SCS part.

- Figure 2: (a): Micro-architecture of the AMO SCS system. (b): Piece-wise linear approximation. (c): Test result of energy efficiency versus throughput.

- D. Cox, “Linear amplification with nonlinear components,” IEEE Trans. on Communications, vol. 22, no. 12, pp. 1942-1945, Dec. 1974. [↩]

- S. Chung, P. A. Godoy, T. W. Barton, E. W. Huang, D. J. Perreault, and J. L. Dawson, “Asymmetric multilevel outphasing architecture for multi-standard transmitters,” IEEE Radio Frequency Integrated Circuits Symposium, pp. 237-240, June 2009. [↩]

- C. P. Conradi, J. G. McRory, and R. H. Johnston, “Low-memory digital signal component separator for LINC transmitters,” Electronics Letters, vol. 36, no. 7, pp. 460-461, Mar. 2001. [↩]

- L. Panseri, L. Romano, S. Levantino, C. Samori, and A. L. Lacaita, “Low-power signal component separator for a 64-QAM 802.11 LINC transmitter,” IEEE Journal of Solid-State Circuits, vol. 43, no. 5, pp. 1274-1286, May 2008. [↩]

- P. K. Meher, J. Valls, J. Tso-Bing, K. Sridharan, and K. Maharatna, “50 Years of CORDIC: Algorithm, architectures, and applications,” IEEE Trans. on Circuits and Systems I: Regular Papers, vol. 56, no. 9, pp. 1893-1907, Sept. 2009. [↩]