High-efficiency, Low-cost Photovoltaics using III-V on Silicon Tandem Cells

- Category: Electronic Devices, Energy, Materials, Nanotechnology

- Tags: eugene fitzgerald, iii-v materials, prithu sharma

Photovoltaics and sustainability have received much attention lately. We seek a tandem photovoltaic device using silicon as both the substrate and lower cell and GaAsP as the upper cell. The ideal band gaps for this two-cell tandem structure with silicon at 1.1eV and GaAsP at 1.75 eV allow access to the highest efficiency possible for a two-cell tandem, 36.5%. The lattice mismatch between GaP and Si is 0.37%; therefore, these two materials constitute a nearly ideal combination for the integration of Si and III–V semiconductor-based technologies. Nevertheless, defect-free heteroepitaxy of GaP on Si has been a major challenge.

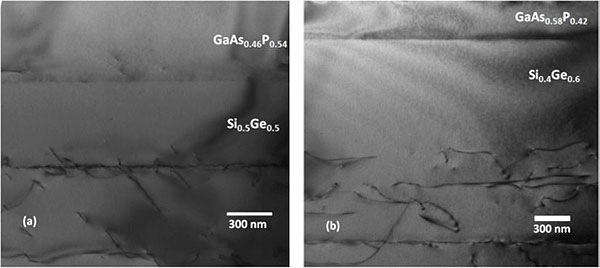

One can envision a process in which a Si1-xGex graded buffer is grown on a Si wafer to extend the lattice parameter part of the way to GaAs, at which point a lattice-matched GaAsyP1-y is grown on the Si1-xGex surface, followed by tensile grading of the GaAsyP1-y until GaP is reached. Identifying the composition where the transition can be made from Si1-xGex to GaAsyP1-y depending on the application is an integral objective of this study. This identification will provide the flexibility to engineer the lattice constants from Si to Ge and GaP to GaAs while maintaining low threading dislocation density (TDD) and surface morphology suitable for device processing. This study has achieved the successful growth of high-quality lattice-matched GaAsyP1-y on Si0.5Ge0.5, Si0.4Ge0.6, and Si0.3Ge0.7 virtual substrates. Various characterization techniques clearly reveal a high-quality crystalline interface (Figure 1) between Si1-xGex and GaAsyP1-y with low TDD suitable for device processing, no rampant dislocation nucleation, anti-phase boundaries, stacking faults or other crystalline defects. Further work will explore the temperature window for the epitaxial growth of GaAsyP1-y on Si1-xGex with higher Si content, as the end goal is to obtain a defect-free GaP film on Si substrate.