DSENT–A Tool for Modeling Opto-electronic Networks-on-Chip

- Category: Circuits & Systems, Optics & Photonics

- Tags: chen sun, vladimir stojanovic

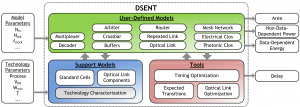

With the rise of many-core chips that require substantial bandwidth from the network-on-chip (NoC), integrated photonic links have been investigated as a promising alternative to traditional electrical interconnects. While numerous opto-electronic NoCs have been proposed, evaluations of photonic architectures have thus far had to use a number of simplifications, reflecting the need for modeling tools and methodologies that accurately capture the tradeoffs for the emerging technology and its impacts on the overall network. To solve these issues, we developed circuit-level models for photonic interconnects [1] and DSENT [2] , a NoC modeling tool for rapid design space exploration of electrical and opto-electrical networks. Using the framework shown in Figure 1, we identified the most profitable opportunities for improvement in the context of an entire opto-electronic network system, emphasizing the impact of photonics technology parameters on the networks at different loads. We find that non-data-dependent laser and tuning power added by photonic components represent a serious source of power inefficiency at lower link utilizations (Figure 2). This inefficiency is problematic as NoCs are typically provisioned to operate well below saturation throughput to achieve low contention delays. We use these results to motivate electrically-assisted tuning strategies [1] [2] and influence photonic network proposals [3] to better address the non-data-dependent power problem of photonics.

- Figure 1: The DSENT modeling framework with some examples of user-defined network models.

- Figure 2: Comparison of network energy per bit vs. network throughput (a) and the energy per bit breakdown at various throughputs (b–d) for an electrical clos network (EClos) and a photonic clos network (PClos) at the 45-nm and 11-nm technology nodes. Utilization is plotted up to the point where the network saturates (defined as the throughput where the latency reaches 3x the zero-load latency).

- M. Georgas, J. Leu, B. Moss, C. Sun, V. Stojanovic, “Addressing link-level design tradeoffs for integrated photonic interconnects,” in Proc. Custom Integrated Circuits Conference, 2011, pp. 1-8. [↩] [↩]

- C. Sun, C-H. Chen, G. Kurian, J. Miller, L. Wei, A. Agarwal, L-S. Peh, V. Stojanovic, “DSENT – A tool connecting emerging photonics with electronics for opto-electronic networks-on-chip modeling,” in Proc. International Symposium of Networks on Chip, 2012. Pp. 201-210. [↩] [↩]

- G. Kurian, C. Sun, C-H. Chen, J. Miller, L. Wei, J. Michel, D. Antoniadis, L-S. Peh, L. Kimerling, V. Stojanovic, A. Agarwal. “Cross-layer energy and performance evaluation of a nanophotonic manycore processor system using real application workloads,” in Proc. International Parallel and Distributed Processing Symposium, 2012. [↩]