Designing Complex Digital Systems with Nano-electro-mechanical Relays

- Category: Circuits & Systems, Electronic Devices, MEMS & BioMEMS

- Tags: hossein fariborzi, vladimir stojanovic

Silicon CMOS circuits have a well-defined lower limit on their achievable energy efficiency due to sub-threshold leakage. Once this limit is reached, power constrained applications will face a cap on their maximum throughput independent of their level of parallelism. Avoiding this roadblock requires an alternative device with steeper sub-threshold slope – i.e., lower VDD/Ion for the same Ion/Ioff. One promising class of such devices is electro-statically actuated nano-electro-mechanical (NEM) switches with nearly ideal Ion/Ioff characteristics. Although mechanical movement makes NEM switches significantly slower than CMOS, they can be useful for a wide range of VLSI applications by reexamining traditional system- and circuit-level design techniques to take advantage of the electrical properties of the device. NEM relay circuits with pass-transistor logic design combine as many propagating electrical delays into as few mechanical delays as possible, parallelizing the tasks to do more operations in less time.

Basic circuit design techniques and functionality of some main building blocks of VLSI systems, such as logic, memory, and clocking structures, have been successfully demonstrated in our previous works [1] [2] [3] .

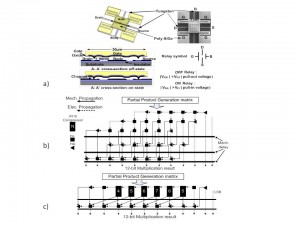

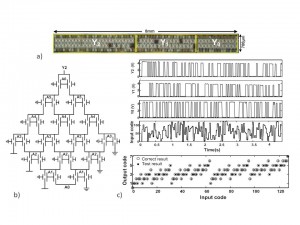

Recently, complex arithmetic units such as relay-based multipliers have been developed (Figure 1b-c) [4] . Simulation results of an optimized 16-bit relay multiplier built in a scaled relay process predicts ~10x improvement in energy-efficiency over optimized CMOS designs in the 10-100 MOPS performance range. The relative performance of the multiplier enhancements are in line with what was previously predicted by a NEM relay 32-bit adder [3] , suggesting that complete VLSI systems (e.g., a microprocessor or an ASIC) would expect to see similar energy/performance improvements from adopting NEM relay technology [3] [4] . The operation of the main building block of the MEM-relay based multiplier, the (7:3) compressor, is experimentally demonstrated. This circuit, consisting of 98 MEM-relays, is the largest MEM-relay based circuit successfully tested to date (Figure 2) [4] .

- Figure 1: (a) SEM, diagram, circuit symbol and operating states of the current MEM relay device, (b) a 6-bit relay multiplier built with full and half adders, and (c) a 6-bit relay multiplier built with (7:3) and smaller compressors.

- Figure 2: (a) The die photo of the (7:3) compressor, (b) the MSB sub-circuit of the (7:3) compressor, and (c) experimental results.

- F. Chen, M. Spencer, R. Nathanael, C. Wang, H. Fariborzi, A. Gupta, H. Kam, V. Pott, J. Jeon, T.K. Liu, D. Marković,V. Stojanović, E. Alon, “Demonstration of Integrated Micro-electro-mechanical Switch Circuits for VLSI Applications,” IEEE International Solid-State Circuits Conference Technical Digest, Feb. 2010, pp. 150-151. [↩]

- H. Fariborzi, M. Spencer, V. Karkare, J. Jeon, R. Nathanael, C. Wang, F. Chen, H. Kam, V. Pott, T.K. Liu, E. Alon, V. Stojanović, D. Marković, “Analysis and Demonstration of MEM-relay Power Gating,” presented at IEEE Custom Integrated Circuits Conference, San Jose, CA, 2010. [↩]

- M. Spencer, F. Chen, C.C. Wang, R. Nathanael, H. Fariborzi, A. Gupta, H. Kam, V. Pott, J. Jeon, T.K. Liu, D. Marković, E. Alon, V. Stojanović, “Demonstration of Integrated Micro-electro-mechanical Relay Circuits for VLSI Applications,” IEEE Journal of Solid State Circuits, Jan. 2011. [↩] [↩] [↩]

- H. Fariborzi, F. Chen, R. Nathanael, J. Jeon, T.K. Liu, V. Stojanović, “Design and Demonstration of Micro-electro-mechanical Relay Multipliers,” presented at IEEE Asian Solid State Circuit Conference, Jeju, S. Korea, 2011. [↩] [↩] [↩]