Continuous-time Delta-sigma Analog-to-digital Converters for Application to Multiple-input Multiple-output Systems

- Category: Circuits & Systems

- Tags: do yeon yoon, hae-seung lee

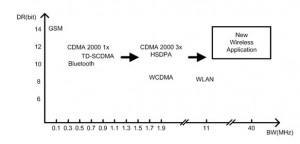

As wireless communication technology is rapidly advancing, new wireless applications are continuously developed. Figure 1 shows each application space and the required dynamic range [1] . The new wireless applications demand wideband (50-MHz) and high resolution data converters (>14 bits). Delta-sigma (ΔΣ) analog-to-digital converters (ADCs) are best suited for their ability to achieve high resolution. However, the large bandwidth required poses a significant challenge. ΔΣ ADCs can be implemented in either a discrete-time (DT) or a continuous-time (CT) structure. Since DT ΔΣ ADCs require op amp settling within each half clock period, the gain-bandwidth requirement for the op amp is extremely high for the sampling rate required for 50MHz bandwidth. The CT ΔΣ ADCs require much lower gain-bandwidth. Thus, CT DS ADCs can function at a higher sampling frequency and achieve a wider bandwidth compared to DT ΔΣ ADCs. In addition, since the CT ΔΣ ADCs are more power-efficient and have an inherent anti-aliasing property, they are more suitable for the demanding new wireless applications

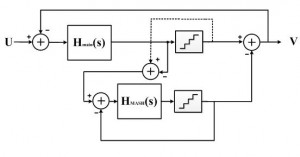

This project focuses on the design of CT ΔΣ ADCs, specifically for the application in multiple-input multiple-output wireless receivers. For this application, each CT ΔΣ ADC in a channel must provide wide bandwidth and high dynamic range at low power consumption. The state-of-art CT ΔΣ ADCs do not come close to achievingwide enough bandwidth and high enough dynamic range for such applications [2] [3] . We are investigating a new type of a CT multi-stage noise-shaping (MASH) ΔΣ ADC based on a DT sturdy-MASH ΔΣ ADC [4] . Figure 2 shows the overall structure of a CT MASH ΔΣ ADC. The main advantage of this new type of CT ΔΣ ADCs is that it does not require digital filters that conventional MASH ΔΣ ADCs need to cancel out the quantization error of the first stage. We have developed several new techniques to make a CT MASH ΔΣ ADC faster, more accurate, and robust.

- Figure 1: Dynamic range and bandwidth requirements of ADCs in wireless applications

- Figure 2: Block diagram of a CT MASH ΔƩ ADC.

- K. Lee, J. Chae, M. Aniya, K. Hamashita, K. Takasuka, S. Takeuchi, and G.C. Temes, “A noise-coupled time-interleaved delta-sigma ADC with 4.2 MHz bandwidth, 98 dB THD, and 79 dB SNDR,” IEEE J. Solid-State Circuits, vol. 43, no. 12, pp. 2601-2612, Dec. 2008. [↩]

- M. Bolatkale, L.J. Breems, R. Rutten, and K.A.A. Makinwa, “A 4GHz CT DS ADC with 70dB DR and −74dBFS THD in 125MHz BW,” ISSCC Dig. Tech. Papers, pp. 470-472, Feb. 2011. [↩]

- G. Mitteregger, C. Ebner, S. Mechnig, T. Blon, C. Holuigue, and E. Romani, “A 20-mW 640-MHz CMOS continuous-time DS ADC with 20-MHz signal bandwidth, 80-dB dynamic range and 12-bit ENOB,” IEEE J. Solid-State Circuits, vol.41, no.12, pp.2641-2649, Dec. 2006. [↩]

- N. Maghari, S. Kwon, and U. Moon, “74 dB SNDR multi-loop sturdy-MASH delta-sigma modulator using 35 dB open-loop Opamp gain,” IEEE J. Solid-State Circuits, vol. 44, no. 8, pp. 2212-2221, Aug. 2009. [↩]