Continuous-time Bandpass Delta-sigma Modulator

- Category: Circuits & Systems

- Tags: hae-seung lee, xi yang

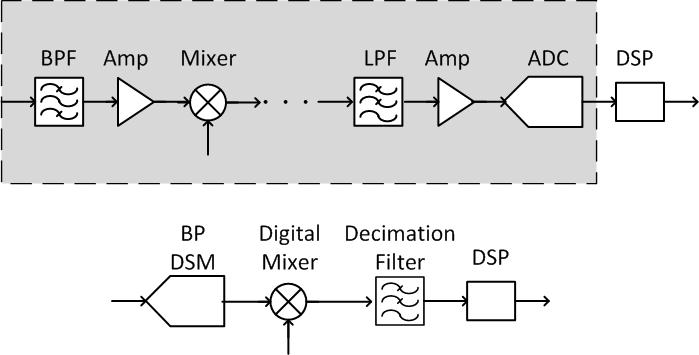

Bandpass delta-sigma modulators (BPDSMs) are particularly useful in modern receiver systems. In a BPDSM system, high-frequency narrow band signals are converted to digital form without prior down-conversion to baseband [1] . This pushes the signal-processing burden to the digital domain and helps improve both system simplicity and power efficiency (Figure 1).

BPDSMs can be realized in either continuous-time (CT) or discrete-time (DT) fashion. The CT structure enjoys three advantages over its DT counterpart [2] : it has the potential to achieve lower noise and better linearity; it relaxes the bandwidth requirement on Opamps; and it provides intrinsic anti-alias filtering. Therefore, this research focuses on the design of CTBPDSM in CMOS technology, aiming to achieve high resolution and large signal bandwidth.

Compared to lowpass (LP) DSMs, BPDSMs require similar clock frequencies for the same oversampling ratio and similar complexity in both the quantizer and the digital-to-analog converter blocks. However, the BPDSM loop filter, which is a bandpass filter with low power and high linearity requirements, is much more challenging to implement [3] . In recent years, several new techniques have been applied to CTLPDSMs that push their performances to wider bandwidth and higher resolution. This research focuses on examining these techniques, adapting them to CTBPDSMs, and investigating the potential for performance improvement. The techniques of interest include the noise-coupled time-interleaved topology [4] , the employment of a voltage-controlled-oscillator-based quantizer [5] , and a cascaded topology [6] .

Figure 1: A signal processing chain found in many receiver systems versus a signal processing chain in a receiver with bandpass analog-to-digital convers

- R. Schreier and G. C. Temes, Understanding Delta-Sigma Data Converters. Hoboken, NJ: John Wiley & Sons. Inc., 2005. [↩]

- K. Philips, “Continuous-time sigma-delta ADCs,” Philips Research Laboratories, Eindhoven, the Netherlands, 2004. [↩]

- C.-Y. Lu, J. F. S.-Rivas, P. Kode, J. S.-Martinez and S. Hoyos “A six-order 200MHz IF bandpass sigma-delta modulator with over 68dB SNDR in 10MHz bandwidth,” IEEE Journal of Solid-State Circuits, vol. 45, no. 6, pp. 1122-1136, Dec. 2010. [↩]

- K. Lee, J. Chae, M. Aniya, K. Hamashita, K. Takasuka, S. Takeuchi and G. C. Temes, “A noise-coupled time-interleaved delta-sigma ADC with 4.2 MHz bandwidth, 98 dB THD, and 79 dB SNDR,” IEEE J. Solid-State Circuits, vol. 43, no. 12, pp. 2601-2612, Dec. 2008. [↩]

- K. Reddy, S. Rao, R. Inti, B. Young, A. Elshazly, M. Talegaonkar and P. K. Hanumolu, “A 16mW 78dB-SNDR 10MHz-BW CT-DS ADC using residue-cancelling VCO-based quantizer,” in Proc. International Solid State Circuit Conference, 2012, pp. 152-153. [↩]

- L. J. Breems, R. Rutten, R. V. Veldohowen, G. V. D. Weide and H. Termeer, “A 56mW CT quadrature cascaded DS modulator with 77dB DR in a near zero-IF 20MHz band,” in Proc. International Solid State Circuit Conference, 2007, pp. 238-239. [↩]