Adaptive Low-power Sensor Interfaces for Wireless Sensor Nodes

- Category: Circuits & Systems

- Tags: anantha chandrakasan, frank yaul

Wireless sensor nodes (WSNs) have a great potential to save energy and improve safety when applied to building energy monitoring, structural monitoring, and environmental monitoring. These systems typically comprise a low-power microprocessor, a wireless transceiver, analog signal conditioning circuits, and an analog-to-digital converter (ADC). However, in order to be sustained by harvested ambient energy, these systems must operate within a tight power budget. Today, circuit blocks like amplifiers and ADCs have individually been highly optimized, but achieving greater power savings requires approaching the system as a whole.

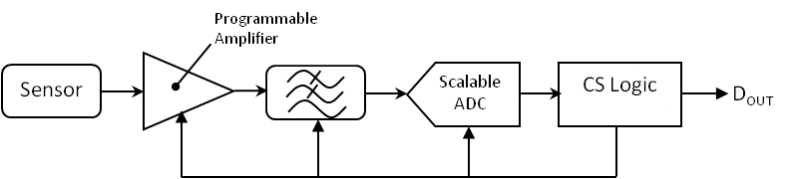

This work focuses on power reduction of the sensor interface circuitry through resolution and sampling frequency scaling [1] and compressed sensing algorithms [2] . Combining the control provided by the algorithms with the scalability designed into the interface circuits creates a fully self-contained adaptive sensor interface that scales its sampling frequency and resolution, among other parameters, based on the local information content of the incoming signal.

- M. Yip and A. P. Chandrakasan, “A resolution-reconfigurable 5-to-10b 0.4V-to-1V power scalable SAR ADC,” IEEE International Solid-State Circuits Conference, Feb 2011, pp. 190-191. [↩]

- F. Chen, A. P. Chandrakasan, and V. M. Stojanovic, “Design and analysis of a hardware-efficient compressed sensing architecture for data compression in wireless sensors, ” IEEE Journal of Solid-State Circuits, vol. 47, no. 3, pp. 744-756, Mar. 2012. [↩]