A Quad Full HD High Efficiency Video Coding Decoder Chip

- Category: Circuits & Systems

- Tags: anantha chandrakasan, chao-tsung huang, hd video

The ever-increasing demand for richer internet video content and larger video resolution has motivated work on algorithms that achieve higher compression without sacrificing visual quality. High Efficiency Video Coding (HEVC) [1] is being developed by the Joint Collaborative Team on Video Coding as a successor to the popular H.264/MPEG-4 AVC standard. For the same quality, HEVC aims for a 50% bit-rate savings over AVC. This improvement comes at the cost of larger coding units, increased complexity through the addition of new coding tools, and increased computation in existing tools.

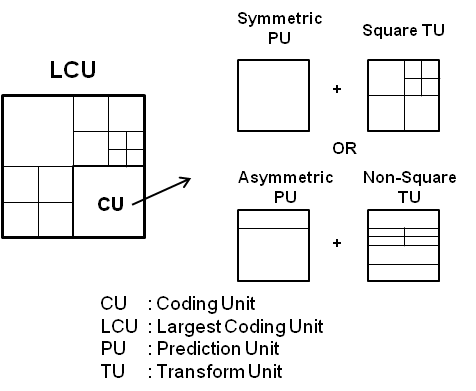

Key features of HEVC include hierarchical coding structures of sizes 64×64 down to 8×8 pixels, 36 intra-prediction modes, asymmetric motion partitions, large and non-square transforms, and multiple concatenated loop filters. This work aims at developing a new system architecture for the hierarchical coding structure along with novel designs for the coding tools themselves. A hybrid system pipeline structure is proposed to support all three largest coding units. The transform block uses SRAM-based 2-D transpose memory and leverages DCT matrix properties for extensive resource-sharing techniques for area reduction. External memory bandwidth and power are major concerns for high definition video decoding. These goals are addressed by a novel cache design with 2-D memory mapping and high throughput.

An HEVC video decoder chip capable of real time Quad Full HD (3840×2160) at 30 fps has been implemented. The decoder supports the HEVC Test Model HM-4.0 with low-complexity entropy coding and both low-delay and random-access encoding profiles.

- B. Bross, W.-J. Han, J.-R. Ohm, G. J. Sullivan, and T. Wiegand, “High efficiency video coding (HEVC) text specification draft 6,” ITU-T SG16 WP3 and ISO/IEC JTC1/SC29/WG11 document JCTVC-H1003, Joint Collaborative Team on Video Coding, San Jose, CA, Feb. 2012. [↩]