Time-to-digital Sensing in Semiconductor Memory: A 1-Mb FRAM in 0.13um CMOS for Low-energy Non-volatile Memory

- Category: Circuits & Systems

- Tags: Anantha Chandrakasan, Masood Qazi

Low-power portable electronics such as implantable medical devices require low-access-energy non-volatile memory to deliver longer battery lifetime and richer functionality. Ferroelectric random access memory (FRAM) technology is a good candidate for both storage and non-volatile RAM (NVRAM) because it provides significant improvement in energy consumption, performance, and endurance compared to current solutions based on FLASH memory technology. The power and supply voltage of FRAM need further reduction in order to achieve the full potential of the technology. This work addresses the challenge of sensing diminishingly small charge and develops circuits compatible with the scaling of FRAM technology to low voltage and more advanced CMOS nodes with a time-to-digital sensing scheme.

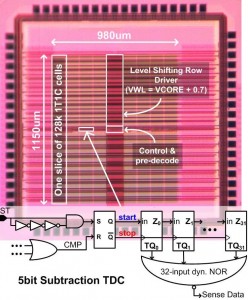

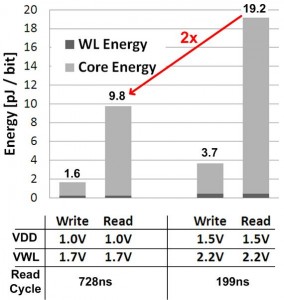

A 1-Mb 1T1C FRAM is designed and fabricated in 130-nm CMOS. Measured results show that performance, spanning 5.03 MHz at 1.5 V to 1.37 MHz at 1.0 V, can be traded off for a reduction in access energy from 19.2 pJ (1.5 V operation) to 9.8 pJ per bit (1.0 V operation). By converting the bitcell charge to a delay, the proposed sensing scheme multiplexes the continuous signal in time simply through a daisy chain of OR gates. Thus 220 1T1C cells multiplex to eight 5-bit time-to-digital converters (TDCs) while preserving 64.4% memory array efficiency. Low voltage operation is enabled by a TDC sensing network that captures the bitcell signal to a finer resolution by digitizing and then subtracting the offset of circuits in the read path. A 128-kb 8T8C design further illustrates the voltage scaling of the sensing network by operating down to 0.8 V with 8.4 pJ access energy. Ultimately, the time-to-digital sensing scheme generalizes across NVRAM technologies as a means to 1) compensate analog offset with digital circuits, 2) operate at low voltage with minimum static power, and 3) better serve the essential multiplexing operation of memory.

- Figure 1: Chip architecture of 1-Mb FeRAM prototype with time-to-digital sensing circuits elucidated.

- Figure 2: Measurement of energy scaling.

- M. Qazi, M. Clinton, S. Bartling, and A. Chandrakasan, “A low-voltage 1Mb FeRAM in 0.13um CMOS featuring time-to-digital sensing for expanded operating margin in scaled CMOS,” IEEE International Solid-State Circuits Conference, pp. 208-209, Feb. 2011.