Highly Parallel Architectures for a Multi-standard Quad-HD Video Encoder

- Category: Circuits & Systems

- Tags: Anantha Chandrakasan, Mahmut Sinangil

The use of video is becoming an important part of today’s world, and consumers are constantly demanding high-definition performance. In today’s market, different video standards featuring different techniques exist (Figure 1), and supporting multiple standards is a necessity. However, video encoding is a computationally intensive process, and battery operated devices such as mobile phones suffer from short battery lives during video encoding. Hence, low-power techniques such as voltage scaling and parallelism need to be applied to video coding [1] to support very high resolution levels for different standards.

In this work, a reconfigurable video encoder supporting both H.264/AVC High Profile Level 5.1 [2] and VC-1 Advanced Profile Level 4.0 [3] standards is designed. The target resolution and frame rate are Quad Full HD (4Kx2K) and 30 fps, respectively. To minimize energy consumption, 0.5 V operation enabled through highly parallel architecture is implemented.

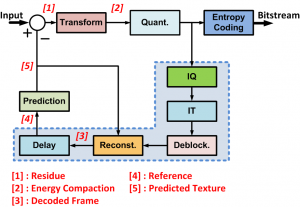

A block diagram of a video encoder is shown in Figure 2. All functional blocks are designed with circuit reconfigurability to support both H.264/AVC and VC-1 standards. Frame and macro-block level parallelism concepts are investigated and implemented to achieve a high throughput constraint at low-voltage levels. The motion estimation block uses data reuse to minimize off-chip data accesses and shares the searching range across multiple macro-blocks. An intra prediction block exploits data dependency to minimize switching activity and matrix factorization to achieve low-power operation. An early mode decision scheme is also implemented to avoid using the motion estimation procedure that is costly in terms of power consumption. Entropy coding block is designed to support the high-levels of parallelism. Overall, a 10X reduction in power consumption is estimated with the proposed techniques.

- Figure 1: Multi-format video content necessitating a video encoder supporting multiple standards.

- Figure 2: Block diagram of a video encoder.

- D. F. Finchelstein, V. Sze, M. E. Sinangil, Y. Koken, and A. P. Chandrakasan, “A low-power 0.7-V H.264 720p video decoder,” IEEE Asian Solid-State Circuits Conference, pp. 173-176, Nov. 2008. [↩]

- “Advanced Video Coding for Generic Audio Visual Services,” ITU-T H.264, Mar. 2009. [↩]

- “VC-1 Compressed Video Bitstream Format and Decoding Process,” SMPTE 421M-2006, Feb. 2006. [↩]