Fully-digital Transmit Equalizer with Dynamic Impedance Modulation

- Category: Circuits & Systems

- Tags: CICS, Ranko Sredojević, Vladimir Stojanovic

In today’s large systems-on-a-chip, communication infrastructure such as high-speed I/Os consumes a significant portion of power, limiting the amount left for useful computation [1] . The conflicting bandwidth and power scaling requirements have stimulated vigorous research activities resulting in significant improvements in link energy-efficiency [2] [3] . These improvements in energy-efficiency have focused on the most dominant sub-systems, such as the clocking and signaling transmit‑receive chain. To that end, voltage-mode (VM) drivers have been introduced instead of current-mode (CM) drivers to improve the energy-efficiency of the transmitter [2] [3] . However, these VM drivers suffer from a power penalty when used to implement a transmit pre-emphasis filter [2] , which is particularly well suited for asymmetric-complexity link channel applications such as memory interfaces [4] and lossy channels with long intersymbol-interference (ISI) tails such as cables or silicon carriers [5] .

In this work, we show that the power penalty incurred by the traditional driver topologies can be tied to the channel impedance matching constraints. Analysis reveals that power-efficiency improvements over the VM transmit-equalization scheme must come from the controlled relaxation of impedance matching constraints on common‑mode and/or differential‑mode matching. One design that makes such a tradeoff, with frequency-selective common‑mode matching for improved power efficiency, appears in [6] . Going a step further, we re-examine the benefits of the static differential impedance matching, and analyze the possible tradeoffs if this constraint is removed, showing that the most efficient driver topology is based on dynamic resistance-modulation (RM) of transmitter impedance.

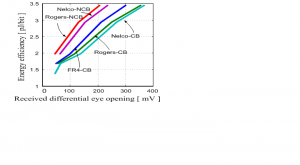

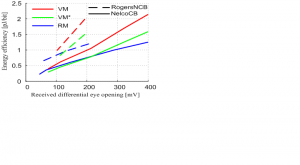

A test chip fabricated in a 90–nm CMOS process shows relatively small signal degradation from dynamic modulation of driver output impedance over a variety of 20” backplanes at 4 Gb/s, with energy-efficiency of 2pJ/bit at 100 mV of receiver eye, in Figure 1. Despite the signal degradation due to impedance mismatch in its operation, the RM driver compares favorably with the traditional driver topologies (CM and different forms of VM driver) in terms of power efficiency, Figure 2, while allowing for a very compact, fully-digital, implementation.

- Figure 1: Energy-efficiency of the RM driver, running at 4 Gb/s, over various backplane channels with Nyquist frequency loss of 8 dB to 12 dB.

- Figure 2: Efficiency comparison between the RM driver and the VM/VM*, assuming appropriately scaled and regulated supply for each driver.

- J. L. Shin, K. Tam, D. Huang, B. Petrick, H. Pham, C. Hwang, H. Li, A. Smith, T. Johnson, and F. Schumacher, “A 40nm 16-core 128-thread CMT SPARC SoC processor,” IEEE Journal of Solid State Circuits, vol. 46, p. 131–144, 2011. [↩]

- H. Hatamkhani and R. Drost, “A 10-mW 3.6-Gbps I/O transmitter,” 2003 Symposium on VLSI Circuits. Digest of Technical Papers (IEEE Cat. No.03CH37408), 2003, pp. 97-98. [↩] [↩] [↩]

- J. Poulton, R. Palmer, A. Fuller, T. Greer, J. Eyles, W. Dally, M. Horowitz, I. Rambus, and C. Hill, “A 14-mW 6.25-Gb/s transceiver in 90-nm CMOS,” IEEE Journal of Solid-State Circuits, vol. 42, p. 2745–2757, 2007. [↩] [↩]

- K. Chang, H. Lee, J.-H. Chun, T. Wu, T. J. Chin, K. Kaviani, J. Shen, X. Shi, W. Beyene, Y. Frans, B. Leibowitz, N. Nguyen, F. Quan, J. Zerbe, R. Perego, F. Assaderaghi, E. C. Real, and L. Altos, “A 16Gb/s/link, 64GB/s bidirectional asymmetric memory interface cell,” 2008 IEEE Symposium on VLSI Circuits, June 2008, pp. 126-127. [↩]

- B. Kim, Y. Liu, T. O. Dickson, J. F. Bulzacchelli, and D. J. Friedman, “A 10-Gb/s compact low-power serial I/O with DFE-IIR equalization in 65-nm CMOS,” IEEE Journal of Solid-State Circuits, vol. 44, no. 12, pp. 3526–3538, Dec. 2009. [↩]

- W. D. Dettloff, J C. Eble, L. Luo, P. Kumar, F. Heaton, T. Stone, and B. Daly, “A 32mW 7.4 Gb/s protocol-agile source-series-terminated transmitter in 45nm CMOS SOI,” Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2010 IEEE International, IEEE, pp. 370–371. [↩]