Continuous-Time Delta-Sigma Analog-to-Digital Converters for Application to a Multiple-Input Multiple-Output System

- Category: Circuits & Systems

- Tags: Do Yeon Yoon, Hae-Seung Lee

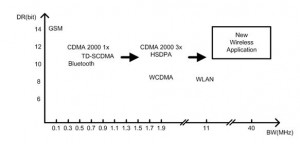

Wireless communication technology is rapidly advancing, and new wireless applications are continuously developed. Figure 1 shows each application and the required dynamic range [1] . The new wireless applications demand wideband and high-resolution data converters. In this situation, delta-sigma (ΔΣ ) analog-to-digital converters (ADCs) are suitable, because they provide low-power and high-resolution characteristics. These ΔΣ ADCs can be implemented in either a discrete-time (DT) or a continuous-time (CT) structure. Since DT ΔΣ ADCs, based on switched capacitors, require op amp settling within each half clock period, the gain-bandwidth requirement for the op amp is rather high. The CT ΔΣ ADCs require much lower gain-bandwidth. Thus, it is possible for CT ΔΣ ADCs to function at higher sampling frequency and achieve wide bandwidth compared to DT ΔΣ ADCs. In addition, since the CT ΔΣ ADCs are more power-efficient and have an inherent anti-aliasing property, they are more suitable for the demanding new wireless applications.

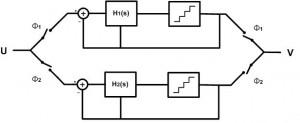

This project focuses on the design of CT ΔΣ ADCs, and specifically for the application in Multiple-Input Multiple-Output wireless receivers. For this application, each CT ΔΣ ADC in a channel must provide wide bandwidth and high dynamic range at low power consumption. Recent state-of-art CT ΔΣ ADCs did not achieve wide enough bandwidth or high enough dynamic range for such application [2] [3] . We are investigating new types of noise-coupled time-interleaved ΔΣ ADCs [1] for MIMO systems. Figure 2 shows the overall structure of noise-coupled time-interleaved ADCs. We are currently investigating techniques that exploit correlation between channels in multi-channel noise coupled system.

- Figure 1: Dynamic range and bandwidth requirements of ADCs in wireless applications.

- Figure 2: The overall structure of noise-coupled time-interleaved ΔƩ ADCs.

- K. Lee, J. Chae, M. Aniya, K. Hamashita, K. Takasuka, S. Takeuchi, and G.C. Temes l., “A Noise-Coupled Time-Interleaved Delta-Sigma ADC With 4.2 MHz Bandwidth, 98 dB THD, and 79 dB SNDR,” IEEE J. Solid-State Circuits, vol. 43, no. 12, pp. 2601-2612, Dec. 2008. [↩] [↩]

- M. Bolatkale, L.J. Breems, R. Rutten, and K.A.A. Makinwa, “A 4GHz CT ΔΣ ADC with 70dB DR and −74dBFS THD in 125MHz BW,” ISSCC Dig. Tech. Papers, pp. 470-472, Feb. 2011. [↩]

- G. Mitteregger, C. Ebner, S. Mechnig, T. Blon, C. Holuigue, E. Romani, A. Melodia, and V. Melini, , “A 14b 20mW 640MHz CMOS CT ΔΣ ADC with 20MHz Signal Bandwidth and 12b ENOB,” ISSCC Dig. Tech. Papers, pp. 131-140, Feb. 2006. [↩]