Compressed Sensing Front-end for Medical Applications

- Category: Circuits & Systems, Medical Electronics

Energy efficiency and power savings are of paramount importance in the ever-increasing use of implantable and portable medical devices. Front-end acquisition ICs are a major component in such devices, comprising mainly instrumentation amplifiers (IA), active analog filters, and analog-to-digital converters (ADCs).

Compressed sensing (CS) [1] has emerged as a promising theory with beneficial implications for data conversion. The Shannon-Nyquist theorem places a great burden on ADCs in terms of power and sampling frequency requirements. However, CS states that if a signal is sparse in a specific basis Ψ, then we do not need as many samples as required by the sampling theorem in order to recover the signal with great accuracy. If implemented before the signal is sampled, this technique effectively allows for a considerable reduction in power consumption by the ADC.

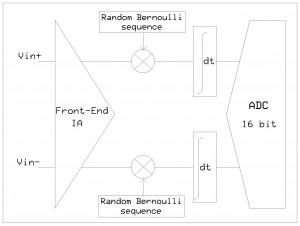

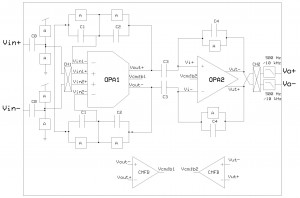

In this work, we explore the benefits of CS with the implementation of a CMOS analog front-end acquisition IC suitable for ECG and pacemaker monitoring devices. ECG signals consist of three main components [2] : the differential ECG signal, the differential electrode offset, and a common-mode signal (mostly at 60 Hz). A high common-mode rejection ratio (CMRR) and low input referred noise are essential in order to extract a clean signal [2] . Figure 1 depicts the overall architecture. The front-end IA (shown in greater detail in Figure 2) consists of a low noise chopper-stabilized IA that consumes 2.73 µW and has 3.86 µVrms of input referred noise, along with a 130-dB CMRR. The triple-slope/SAR ADC simulations are currently underway.

- Figure 1: Block diagram of overall architecture.

- Figure 2: Front-end IA circuit diagram. OPA1 consists of a telescopic op-amp while OPA2 consists of a folded op-amp. Squares with “A” represent pseudo-resistors.

- E. J. Candès, “Compressive sampling,” in Proc. International Congress of Mathematicians, Madrid, Spain, 2006. [↩]

- K. Soundarapandian and M. Berarducci, 2010, Apr. 15, “Analog front-end design for ECG systems using delta-sigma ADCs,” [Online]. Available: http://www.ecnmag.com/Articles/2010/04/Analog-Front-End-Design/ [↩] [↩]