Compressed Sensing for Implantable Sensors

- Category: Circuits & Systems

- Tags: Anantha Chandrakasan, CICS, Fred Chen, Vladimir Stojanovic

Implantable medical sensors are an emerging application area that exemplifies the stringent energy constraints imposed on wireless sensor circuits. In typical circuit blocks used for medical monitoring, the cost to wirelessly transmit data is orders of magnitude greater than for any other function. State-of-the-art radio transmitters exhibit energy-efficiencies in the nJ/bit range while every other component consumes at most only 10’s of pJ/bit. This cost disparity suggests that some data reduction strategy at the sensor node should be employed to minimize the energy cost of the system. Existing strategies for implementing integrated data compression or filtering solutions under these constraints largely revolve around detecting and extracting specific signal data [1] [2] [3] . However, the filtered data often contains limited information. For these signal processing strategies, there is a tradeoff between data reduction, robustness, implementation cost, and the granularity of information captured. In each case, the goal is to minimize the number of bits transmitted (to minimize the average radio power) while reliably preserving the signal information at a minimum implementation cost.

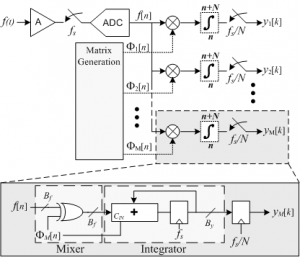

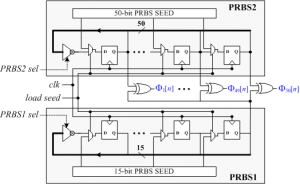

In this work, we introduce the design and implementation of a sensor compression architecture (Figure 1) based on the theory of compressed sensing (CS) [4] that offers an improved set of tradeoffs toward achieving this goal. A CS-based sensor system combines the positive qualities of existing data acquisition and compression systems: it provides a flexible and general interface like an analog-to-digital converter (ADC) yet still enables data compression proportional to the signal information content, which is consistent with the performance of source coding. For wireless sensor applications, this combination of characteristics is particularly attractive as it would enable a single hardware interface across many applications while simultaneously addressing the energy cost of the wireless telemetry. This approach reduces the average radio power by exploiting signal sparseness to encode the data at a high compression factor (>10x) while enabling a faithful reconstruction of the entire original signal. An efficient implementation of the CS encoder and encoder matrix generation (Figure 2) is realized and demonstrated in a 90-nm CMOS process and consumes 1.9 µW at 0.6 V and 20 kS/s [5] .

- Figure 1: Block diagram and circuitry for the implementation of the CS linear transform encoder.

- Figure 2: Implementation of the CS matrix generation.

- R. Harrison, P. Watkins, R. Kier, R. Lovejoy, D. Black, B. Greger, and F. Solzbacher, “A low-power integrated circuit for a wireless 100-electrode neural recording system,” IEEE Journal of Solid-State Circuits, vol. 42, pp. 123-133, 2007. [↩]

- R. Olsson and K. Wise, “A three-dimensional neural recording microsystem with implantable data compression circuitry,” IEEE Journal of Solid-State Circuits, vol. 40, pp. 2796-2804, 2005. [↩]

- N. Verma, A. Shoeb, J. Bohorquez, J. Dawson, J. Guttag, and A.P. Chandrakasan, “A micro-power EEG acquisition SoC with integrated feature extraction processor for a chronic seizure detection system,” IEEE Journal of Solid-State Circuits, vol. 45, pp. 804-816, 2010. [↩]

- D. Donoho, “Compressed sensing,” IEEE Transactions on Information Theory, vol. 52, pp. 1289–1306, 2006. [↩]

- F. Chen, A.P. Chandrakasan, and V. Stojanovic, “A Signal-agnostic compressed sensing acquisition system for wireless and implantable sensors,” presented at IEEE Custom Integrated Circuits Conference, San Jose, CA, 2010. [↩]