A Low-power 32-channel Digitally-programmable Neural Recording System

- Category: Circuits & Systems, Medical Electronics

- Tags: Rahul Sarpeshkar

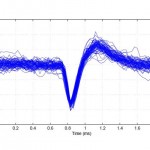

We have designed an ultra-low-power 32-channel neural recording system in a 0.18-µm CMOS technology. The system consists of eight neural recording modules; each module contains four neural amplifiers, an analog multiplexer, an A/D converter, and a serial programming interface. Each amplifier can be programmed to record either spikes or LFPs with a programmable gain from 49-66 dB. To minimize the total power consumption, an adaptive-biasing scheme is utilized to adjust each amplifier’s input-referred noise to suit the background noise at the recording site. The amplifier’s input-referred noise can be adjusted from 11.2 µVrms (total power of 5.4 µW) down to 5.4 µVrms (total power of 20 µW) in the spike recording setting. The ADC in each recording module digitizes the signal from each amplifier at 8-bit precision with a sampling rate of 31.25 kS/s per channel and an average power consumption of 483 nW per channel. It achieves an ENOB of 7.65, resulting in a net efficiency of 77 fJ/State, making it one of the most energy-efficient designs for neural recording applications. The presented system was successfully tested in an in-vivo wireless recording experiment from a behaving primate with an average power dissipation per channel of 10.1 µW. The neural amplifier and the ADC occupy the areas of 0.03 mm2 and 0.02 mm2, respectively, making our design simultaneously area-efficient and power-efficient.

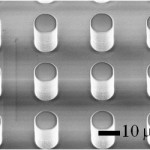

- Figure 1: System architecture of the 32-channel neural recording IC.

- Figure 2: Superimposed digitized neural waveforms from one of the recording channels.

- W. Wattanapanitch and R. Sarpeshkar, “A low-power 32-channel digitally-programmable neural recording system,” IEEE Transaction on Biomedical Circuits and Systems, 2011, accepted for publication.