# A Through-Wafer Interconnect in Silicon for RFICs

Joyce H. Wu, Jörg Scholvin, and Jesús A. del Alamo

Abstract—In order to minimize ground inductance in RFICs, we have developed a high-aspect ratio, through-wafer interconnect (or substrate via) in silicon that features a silicon nitride barrier liner and completely filled Cu core. We have fabricated vias with a nominal aspect ratio of 30 and verified the integrity of the insulating liner in vias with an aspect ratio of eight. The inductance of vias with nominal aspect ratios between three and 30 approach the theoretically expected values. This interconnect technology was exploited in a novel Faraday cage structure for substrate crosstalk suppression in system-on-chip applications. The isolation structure consists of a ring of grounded vias that surrounds sensitive or noisy portions of a chip. This Faraday cage structure has shown noise suppression of 30 dB at 10 GHz and 16 dB at 50 GHz at a distance of 100  $\mu$ m when compared to the reference structure.

*Index Terms*—Ground inductance, Si RF technology, substrate noise, substrate via, system-on-chip (SOC), three-dimensional interconnects, through-wafer interconnect.

#### I. INTRODUCTION

N MILLIMETER-WAVE and RF applications, the high-frequency performance of silicon-based technology has been approaching that of III-V semiconductor devices in recent years. Consequently, silicon is replacing GaAs in low-end, high-volume RF applications because of its lower manufacturing costs and its integration capabilities [1]. To improve the high-frequency operation of silicon RFICs, it is crucial to reduce extrinsic parasitics. In particular, the source impedance of MOSFETs and the emitter impedance of BJTs degrade the gain, noise figure, and efficiency of RF amplifiers [2]-[4]. Through-wafer interconnects, or substrate vias, are widely used in GaAs microwave and millimeter-wave ICs to provide a low-impedance ground to reduce the source impedance [3], [4]. Extending this idea to silicon, we have developed a through-wafer via technology for silicon, which allows for the implementation of high-aspect ratio, low-impedance ground connections.

Through-wafer vias in silicon have initially been demonstrated using KOH etching [5], [6]. However, this approach results in a poor aspect ratio with a large footprint at the wafer surface. Borrowed from microelectromechanical systems (MEMS) technology, we have used deep reactive-ion etching (DRIE), which can achieve aspect ratios of up to 20 and has become a common method to etch through-wafer vias in silicon. Recently, electrochemical etching has been used to form porous Si that can produce vias of aspect ratios of 100 [7], [8]. Previous DRIE-via technologies use a thin coating of metal to line the inside surface of the via [9], [10], whereas others fill the via with highly doped polysilicon to achieve a low-impedance interconnect [11]. These different via technologies have found applications in three-dimensional (3-D) chip stacks [5], as a substrate coil inductor [9], microstrip substrate interconnect [10], and in MEMS [7], [11]. The novelty of our via technology is that it features an insulator liner and a solid metal core. Consequently, the vias exhibit very low impedance over a broad frequency range, which is essential for use in mixed-signal RF systems. They can also be used to distribute power and ground in logic circuits and MEMS. In order to characterize this technology, we have fabricated test structures that measure the impedance of a single via in the microwave regime.

In exploring other practical applications, we have exploited this via technology to construct an innovative isolation scheme to reduce substrate crosstalk in mixed-signal circuits for system-on-a-chip (SOC) applications [12]. Early results of this technology characterized up to 6 GHz were published in [13]. This paper discusses the details of the fabrication process of the substrate vias and gives more extensive results of isolated vias and Faraday cages up to 50 GHz.

## **II. FABRICATION TECHNOLOGY**

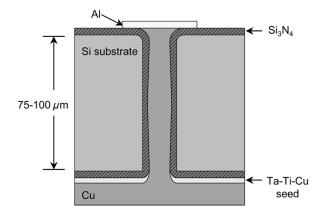

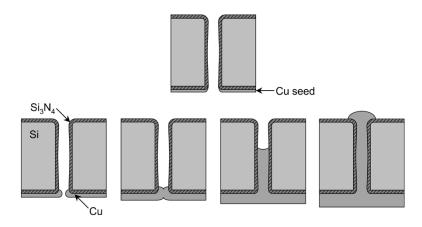

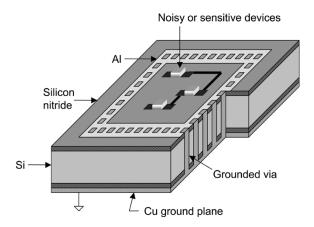

This paper exploits MEMS technology to develop a through-wafer via technology for applications in thin substrates and fabrication at the back-end. There are three critical process steps: 1) DRIE of Si to form vias; 2) conformal deposition of silicon nitride to line the vias; and 3) Cu electroplating and CMP to fill the vias and prepare them for metal contacts. An illustration of the via concept is depicted in Fig. 1. In order to fabricate substrate vias on thin substrates without using such fragile starting material, we developed a test vehicle on thick-film, bonded silicon-on-insulator (SOI) wafers. The SOI device layer, 75- to 100- $\mu$ m thick, was intended as the substrate for via fabrication, whereas the handle wafer strengthened wafer integrity. Holes were etched in the handle wafer from the backside using KOH, and the buried oxide was etched using BOE. These holes gave access to the underside of the device layer while still maintaining wafer integrity. The backside holes and SOI handle wafer were intended only for handling purposes and are not part of the substrate-via structure.

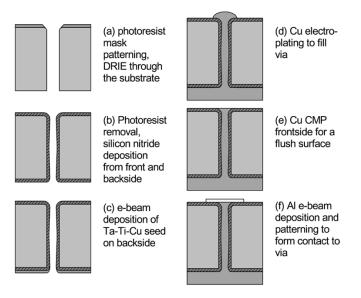

Both trenches and vias were etched in order to facilitate the characterization of the fabrication process. Substrates had a resistivity of 10–20  $\Omega \cdot \text{cm}$ . In the following paragraphs, we give details about each of the key process steps in our technology. The process flow is depicted in Fig. 2.

Manuscript received April 13, 2004; revised August 27, 2004. This work was supported in part by the SRC, in part by MARCO Interconnect Focus Center, and in part by Intel Corporation. The review of this paper was arranged by Editor R. Shrivastava.

The authors are with the Massachusetts Institute of Technology, Cambridge, MA 02139 USA (e-mail: jowu@mtl.mit.edu).

Digital Object Identifier 10.1109/TED.2004.837378

Fig. 1. Conceptual drawing of a substrate via.

Fig. 2. Sketch of the process flow to fabricate through-wafer vias.

## A. Silicon DRIE

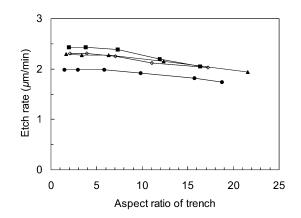

The vias were etched through the substrate (SOI device layer) from the frontside using an STS anisotropic deep reactive-ion etcher (DRIE) with an inductively coupled plasma. The DRIE uses a Bosch etch of alternating etch and passivation cycles to achieve near-vertical sidewalls to create high-aspect ratio structures [14]. A 3- $\mu$ m-thick OCG825 photoresist was used as the mask. The etch rate was about 2  $\mu$ m/min, and trench aspect ratios as high as 49 were achieved. As in [14], we found that the etch rate decreased with increasing aspect ratio. Our results, depicted in Fig. 3, show that the dependence was noticeable but small, and that for aspect ratios as high as 20, the decrease in etch rate was less than 15%. This dependence is due to reactive-ion etch lag (RIE-lag) common in fluorinated plasmas [14].

Another consequence of DRIE is that the via opening widens as the etch proceeds due to the slant in the photoresist profile. We found that the via diameter increases by about 1  $\mu$ m for every 100  $\mu$ m etched in depth. This produces a small difference between the nominal diameter on the mask and the actual physical diameter of the via, and consequently, discrepancies in the nominal and actual aspect ratio. In this paper, actual aspect ratios will be quoted unless noted otherwise.

Fig. 3. DRIE etch rate versus aspect ratio for trenches on different wafers (each line). For aspect ratios as high as 20, the decrease in the etch rate is less than 15%.

#### B. Silicon Nitride Insulating Barrier Liner

Our goals in introducing a via liner were twofold. First, the liner must be a barrier to the Cu that fills the via because migrating Cu ions degrade device performance by inducing leakage currents [15]. Second, in order to route power and ground on the same chip, the substrate vias must be electrically insulated from the Si substrate. Amorphous dielectric films like Si<sub>3</sub>N<sub>4</sub> and SiO<sub>x</sub>N<sub>y</sub> meet both criteria [16]. Since our process is designed so that the substrate-via fabrication is part of the backend, we deposited Si<sub>3</sub>N<sub>4</sub> by plasma-enhanced chemical vapor deposition (PECVD) at 400 °C using a Novellus Concept-1. This tool combines the stable discharge and substrate coupling of high frequency plasma and the low-energy ion bombardment of low frequency for better sidewall density and step coverage [17].

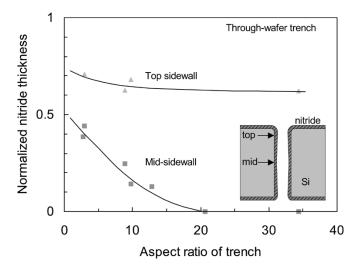

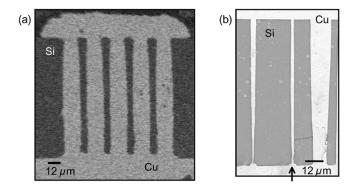

To take advantage of the insulating and barrier properties of silicon nitride, the liner had to be conformal to the sidewalls of the via. To improve conformality, we deposited nitride on the frontside and backside. We characterized the conformality of PECVD silicon nitride by examining cross sections of silicon nitride deposited in through-wafer trenches. Fig. 4 plots the nitride sidewall thickness normalized to the surface thickness against the aspect ratio of through-wafer trenches. Thickness measurements were taken using the SEM at the top sidewall 1  $\mu$ m from the surface and at the mid-sidewall. Fig. 4 shows that the nitride thickness at the top of the sidewall remains relatively constant, independent of aspect ratio (top line in Fig. 4). However, the thickness at the mid-sidewall decreases drastically, thinning with aspect ratio (bottom line). For aspect ratios greater than 15, the nitride was too thin or nonexistent in the middle of the trench. The highest aspect ratio trench fully lined with conformal nitride was 10. For vias, it was eight [Fig. 5(a)]. In this process, silicon nitride conformality has emerged as the limiting factor for achieving fully lined vias with higher aspect ratios. However, other deposition methods may provide better conformality.

# C. Cu Electroplating

The low resistivity of Cu allows for higher current density, and Cu has proven to have increased scalability and better electromigration reliability than Al(Cu) interconnects [18]. Some

Fig. 4. Normalized PECVD silicon nitride liner thickness versus aspect ratio of a through-wafer trench. The liner thickness is normalized to the surface thickness. Mid-sidewall measurements were taken halfway down the trench and top sidewall measurements 1  $\mu$ m down from the surface.

Fig. 5. (a) SEM cross section of substrate vias with an aspect ratio of 8, 12- $\mu$ m-wide via in a 100- $\mu$ m-thick substrate. These vias are conformally lined with silicon nitride and overfilled with Cu (SEM taken prior to the CMP step). (b) Best DRIE and Cu electroplating result (arrow): a trench of aspect ratio 49, 2- $\mu$ m wide by 97- $\mu$ m deep, filled with Cu without seams or voids. The "footing" at the bottom of these trenches is from a previous process in which the buried oxide was used as an etchstop for the DRIE.

disadvantages of Cu are its poor adhesion to dielectrics and the need for barrier and/or adhesion layers [18]. However, Cu has the critical advantage of being able to fill high-aspect ratio holes by electroplating.

We used a commercial Cu-sulfate solution from Enthone-OMI that is used for semiconductor applications and particularly for high-aspect ratio plating. We used a Dynatronix DuPR 10-1-3 power supply with a pulse-reverse current, which enhances electrodeposition into high-aspect ratio structures. The dissolution of Cu during the negative pulse provides a better concentration gradient of cupric ions in the via than dc, so that during the subsequent positive pulse, deposition is more uniform and void size is reduced [19]. We used a positive peak pulse of 16 mA/cm<sup>2</sup> for 5 ms and a negative peak pulse of -13 mA/cm<sup>2</sup> for 1 ms, which equates to an average current density of 11 mA/cm<sup>2</sup>.

For our electroplating seed, we e-beam evaporated a stack of 250 Å Ta, 250 Å Ti, and 2000 Å of Cu onto the wafer backside. Due to the anisotropy of e-beam deposition and the high-aspect

ratio of the vias, the seed did not significantly coat the via sidewalls, and as a result, the seed was perforated. During copper electroplating, Cu deposited onto the seed at the bottom of the via increased in thickness isotropically until the opening closed (Fig. 6). Once the via bottom was sealed, the inside of the via filled from bottom to top. This process resulted in a solid Cu core without seams and voids, as similarly reported in [19].

The rate of filling of the via had a slight inverse dependence on the opening width. This is due to initial time taken to seal the bottom of the via. Larger diameter vias will take longer to seal, and therefore will fill slower. Additionally, the Cu deposition rate varied across the wafer. By overfilling the vias and using chemical–mechanical polishing (CMP) to remove excess Cu, we were able to obtain a Cu filling that was flush with the surface for all via dimensions across the wafer and eliminated the dependence on a uniform Cu deposition rate. Contact to the via at the top was made through a patterned Al layer. The highest aspect ratio trench filled with Cu was 49 [Fig. 5(b)], and 14 for vias, although it is possible to achieve even higher aspect ratios.

# III. APPLICATION I: THROUGH-WAFER VIA INTERCONNECT

#### A. Test Structure and Measurement Setup

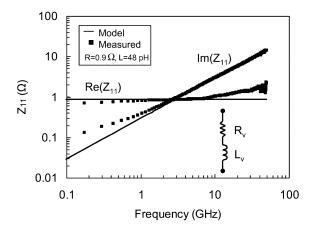

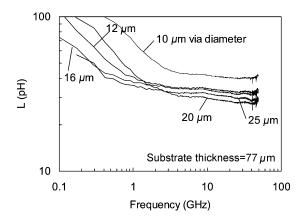

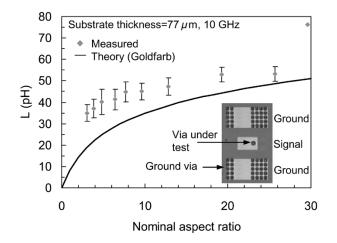

To measure the impedance of a single via, we designed a oneport, 50- $\Omega$ , ground-signal-ground coplanar test structure with the via under test at the end of the signal line (Fig. 9 inset). The ground pads are shorted by 30 substrate vias to the backside Cu ground plane in order to reduce the impedance of the ground pads. Characterized vias ranged from 3 to 25  $\mu$ m in nominal diameter on a 77- $\mu$ m-thick substrate. S-parameters of the substrate vias were measured from 50 MHz to 50 GHz and converted to  $Z_{11}$ . The series resistance and inductance of the test structure pads were not de-embedded, so the actual impedance of a via is lower than that measured. The test structure parasitics are estimated to contribute less than 4 pH to the inductance values.

# B. Results and Discussion

For all vias, the real part of  $Z_{11}$  was found to be largely independent of frequency (below about 5 GHz), whereas the imaginary part was positive and increased linearly with frequency (Fig. 7). These results suggest a simple, equivalent circuit model for a via that consists of a resistor and an inductor in series, from which the inductance was extracted. The rise in the real part at frequencies greater than 5 GHz represents an increase in resistance due to the skin effect. The skin effect is also responsible for the decline in inductance as seen in Fig. 8. This is because the effective area enclosed by the current loop is reduced due to surface current crowding. As seen in the Fig. 8, larger diameter vias are affected by the skin effect at lower frequencies.

Fig. 9 shows the averaged measured inductances of substrate vias at 10 GHz against the nominal aspect ratio along with the inductance predicted by [20]. The measured inductance values are tightly clustered and approach the theoretical curve. This suggests that it is possible to predict inductance values for a particular aspect ratio via for computer-aided circuit design tools.

Fig. 6. Sketch of the evolution of the electrodeposition of Cu with perforated seed. Starting from the seed evaporated on the backside in Fig. 2(c), the electroplated Cu deposits isotropically on the seed. The Cu deposit grows horizontally until the Cu on the two sides of the via meet, sealing the via opening at the bottom. Then, the Cu deposits inside the via filling it and on the backside.

Fig. 7.  $Z_{11}$  versus frequency of a 4- $\mu$ m diameter and 77- $\mu$ m-deep via. The solid line plots simulation results of a series *RL* equivalent circuit model from which the indicated values of resistance and inductance are extracted. The slight rise in resistance with frequency is due to the skin effect.

Fig. 8. Inductance extracted from the imaginary part of  $Z_{11}$  versus frequency. The inductance decreases with frequency due to the skin effect.

The residual discrepancy of the inductance with [20] may be due to parasitic inductance of the test structure or the assumptions made in the development of the model.

Fig. 9. Extracted inductance at 10 GHz versus nominal aspect ratio of vias on a substrate thickness of 77  $\mu$ m. Each point represents the average inductance with error bars of one standard deviation in each direction. Plotted in a solid line is the inductance model of Goldfarb *et al.* [20]. *Inset*: picture of fabricated test structure to measure inductance of a single via. The multiple grounding vias reduce the impedance of the ground pads.

# IV. APPLICATION II: FARADAY CAGE FOR SUBSTRATE CROSSTALK SUPPRESSION

# A. Motivation

One of the possible applications of high-aspect ratio substrate vias is subsystem isolation in mixed-signal circuits. Substrate crosstalk between sensitive RF circuits, analog circuits, and noisy digital blocks is a significant barrier to enabling one-chip systems. Future systems will require densely packed circuits operating at high frequency. This has motivated substantial work in the development of substrate crosstalk isolation schemes [6], [8], [21]–[25].

Traditional approaches to reduce substrate crosstalk include guard rings [21], [22], SOI and high-resistivity substrates [22]–[24], and junction-isolated wells [22]. However, unconventional techniques have achieved better crosstalk suppression, such as porous silicon [7], [8], metal-filled trenches [6], and SOI on metal with Faraday cage [25]. A comparison between different crosstalk isolation schemes is difficult due to different

Fig. 10 Faraday cage as a novel isolation scheme for substrate crosstalk. The ring of grounded vias surrounds a noisy or a sensitive circuit.

references structures and test structure design. A key consideration when evaluating crosstalk isolation schemes is the footprint of the isolation structure and nonstandard fabrication processes. For example, in [6] the metal trench is 60- $\mu$ m wide and in [8] 100- $\mu$ m wide, and [25] uses a buried metal ground.

We have exploited the high-aspect ratio of our substrate vias to demonstrate a novel Faraday cage isolation scheme to suppress substrate crosstalk [12]. The Faraday cage consists of a ring of substrate vias connected to the grounded backplane on the backside of the substrate and shorted together by a ring of metal on the frontside (Fig. 10). This approach combines exceptional crosstalk suppression with a small footprint.

#### B. Test Structure and Measurement Setup

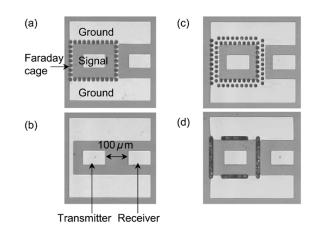

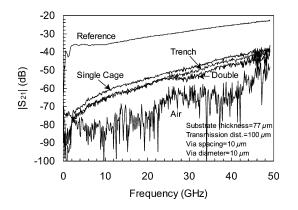

To determine the isolation effectiveness of the Faraday cage, we measured  $S_{21}$  up to 50 GHz using a two-port test structure in a coplanar, 50- $\Omega$  ground-signal-ground configuration (Fig. 11). The distance between the pads varied from 100 to 800  $\mu$ m, and the transmitter pad was surrounded by the Faraday cage. The transmitter and receiver pads were each  $62 \times 100 \ \mu m$  in area. An identical structure was fabricated without the Faraday cage, but with the same grounded backplane, to serve as the reference [Fig. 11(b)]. Additional Faraday cage variations were examined: a double Faraday cage [Fig. 11(c)] and a discontinuous trench [Fig. 11(d)]. The double Faraday cage had one cage encircling the other, with each ring separated by 10  $\mu$ m. The trench Faraday cage was 10  $\mu$ m wide and was discontinuous in order to maintain the integrity of the substrate. In this implementation, we used a 77- $\mu$ m-thick substrate and 10- $\mu$ m-diameter vias with an aspect ratio close to 8. We also varied via spacing between 10 and 70  $\mu$ m on test structures with a transmission distance of 200  $\mu$ m. We had to reduce the air crosstalk between the microwave probes in order to accurately determine the crosstalk suppression of the Faraday cage. For this, we introduced a grounded metallic screen between the two probes that reduced crosstalk through the air by about 30 dB. The noise floor of our setup was reduced to around -90 dB at 1 GHz and -47 dB at 50 GHz at a probe separation distance of 100  $\mu$ m.

Fig. 11. Top view of (a) a Faraday cage test structure; (b) a reference test structure; (c) a double Faraday cage; and (d) a trench Faraday cage at a transmitter-receiver separation or transmission distance of  $100 \,\mu$ m. Each via of the cage is  $10 \,\mu$ m wide and separated by  $10 \,\mu$ m. For the double Faraday cage, the ring of cages is separated by  $10 \,\mu$ m.

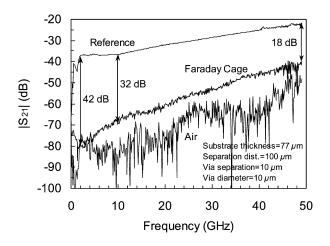

Fig. 12.  $|S_{21}|$  versus frequency for a Faraday cage and reference structure at a transmission distance of 100  $\mu$ m. This Faraday cage provides 32 dB of isolation at 10 GHz and 18 dB at 49 GHz. Also plotted is  $|S_{21}|$  of the probes in the air.

# C. Results and Discussion

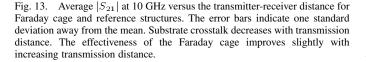

Fig. 12 graphs  $|S_{21}|$  against frequency for a Faraday cage at a transmission distance of 100  $\mu$ m. Also shown are measurements from the reference structure and with the probes lifted in the air to show that the measurements are not limited by air crosstalk. Compared to the reference structure, on average, the Faraday cage improved isolation by 30 dB at 10 GHz and 16 dB at 50 GHz. Comparing the reference structure to one with a 20- $\mu$ m wide metal Al strip between the transmitter and receiver produced only about 2 dB in isolation. Fig. 13 shows the impact of transmitter-receiver separation on crosstalk isolation at 10 GHz. On average, the Faraday cage improved isolation by 30 dB at 100  $\mu$ m and 42 dB at 800  $\mu$ m when compared to the reference. The reference structure shows an expected decrease in crosstalk with distance, and the Faraday cage shows an improvement in crosstalk suppression of about 12 dB as the distance is increased from 100 to 800  $\mu$ m.

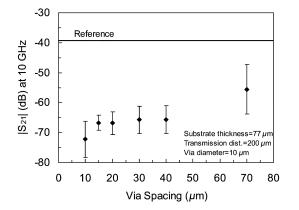

We have also examined the impact of via separation on isolation effectiveness. For a transmission distance of 200  $\mu$ m, we fabricated Faraday cages with via spacings between 10 and

the mechanical integrity of the substrate without compromising

crosstalk suppression. To determine if other types of Faraday cage structures would

improve its performance, we fabricated a double Faraday cage, and a Faraday cage constructed by a discontinuous trench as seen in Fig. 11. The results of the crosstalk measurements are plotted in Fig. 15. The single and double cage and trench perform within about 3 dB overall. This result, together with the via spacing results suggest that a simple cage of sparse substrate vias can significantly reduce crosstalk through the substrate. Further insight into the noise suppression of the Faraday cage can be obtained by deriving a lumped-element equivalent circuit model, which has been presented in [26].

# V. CONCLUSION

We have successfully developed a high-aspect ratio, insulated substrate-via technology in silicon and have used these vias to demonstrate a new Faraday cage isolation scheme for SOC applications. We have demonstrated fully lined and completely filled substrate vias with aspect ratios of 8. Measured inductance of individual vias approaches theoretically expected values. We have used this substrate-via technology to demonstrate a Faraday cage isolation scheme for SOC applications. The Faraday cage improves isolation by 30 dB at 10 GHz and 16 dB at 50 GHz at a distance of 100  $\mu$ m. The small footprint of the isolation structure and its high isolation effectiveness at short distances allows close packing of mixed-signal circuits.

#### ACKNOWLEDGMENT

The authors wish to thank J. G. Fiorenza, A. A. Ayón, J. Voldman, A. Fan, D. A. Hitko, K. A. Jenkins, and the staff at the Microsystems Technology Laboratories at MIT for fabrication and measurement advice.

#### REFERENCES

- [1] A. Matsuzawa, "RF-SoC-Expectations and required conditions," IEEE Trans. Microwave Theory Tech., vol. 50, pp. 245-253, Mar. 2002.

- M. Fukuta, K. Suyama, H. Suzuki, and H. Ishikawa, "GaAs microwave [2] power FET," IEEE Trans. Electron Devices, vol. ED-23, pp. 388-394, 1976.

- [3] R. A. Pucel, "Design considerations for monolithic microwave circuits," IEEE Trans. Microwave Theory Tech., vol. MTT-29, pp. 513-534, Apr., 1981.

- [4] H. Furukawa, T. Fukui, T. Tanaka, A. Noma, and D. Ueda, "A novel fabrication process for surface via-holes for GaAs power FETs," in Proc. IEEE GaAs Conf., 1998, pp. 251-254.

- [5] S. Linder, H. Baltes, F. Gnaedinger, and E. Doering, "Fabrication technology for wafer through-hole interconnections and three-dimensional stacks of chips and wafers," in Proc. MEMS, 1994, pp. 349-354

- [6] N. P. Pham, K. T. Ng, M. Bartek, P. M. Sarro, B. Rejaei, and J. N. Burghartz, "A micromachining post-process module for RF silicon technology," in IEDM Tech. Dig., 2000, pp. 481-484.

- [7] L. Wang, A. Nichelatti, H. Schellevis, C. de Boer, C. Visser, T. N. Nguyen, and P. M. Sarro, "High aspect ratio through-wafer interconnections for 3-D microsystems," in Proc. MEMS, 2003, pp. 634-637.

- [8] H. S. Kim, K. Chong, Y.-H. Xie, and K. A. Jenkins, "The importance of distributed grounding in combination with porous Si trenches for the reduction of RF crosstalk through p- Si substrate," IEEE Electron Device Lett., vol. 24, pp. 640-642, June 2003.

- [9] H. T. Soh, C. P. Yue, A. M. McCarthy, C. Ryu, T. H. Lee, and C. F. Quate, "Ultra-low resistance, through-wafer via (TWV) technology and its applications in three dimensional structures in silicon," in Proc. Int. Conf. Solid State Devices Materials, 1998, pp. 284-285.

400

Transmission Distance (µm)

Reference

Faraday Cage

200

Substrate thickness=77 µm Via spacing=10 µm

Via diameter=10 um

600

800

Fig. 14. Average  $|S_{21}|$  versus via spacing of the Faraday cage at 10 GHz. No crosstalk dependence is apparent up to a 40- $\mu$ m separation.

Fig. 15.  $|S_{21}|$  versus frequency for a single, double, and trench Faraday cage and reference structure at a transmission distance of 100  $\mu$ m. Crosstalk suppression is within 3 dB for all three types of Faraday cages across the entire spectrum.

70  $\mu$ m. Fig. 14 plots the average crosstalk suppression for these via spacings at 10 GHz. We found that there is no discernible dependence of isolation effectiveness on via density for via spacings up to 40  $\mu$ m. At 70- $\mu$ m via spacing, the degradation in crosstalk suppression is about 10 dB. This is an important result because sparse Faraday cages can be used in order to maintain

-20

-30

-40

-50

-60

-70

-80

-90

-100

0

S21 (dB) at 10 GHz

- [10] K. M. Strohm, P. Nuechter, C. N. Rheinfelder, and R. Guehl, "Via hole technology for microstrip transmission lines and passive elements on high resistivity silicon," in *Proc. IEEE MTT-S Int. Microwave Symp.*, 1999, pp. 581–584.

- [11] E. M. Chow, V. Chandrasekaran, A. Partridge, T. Nishida, M. Sheplak, C. F. Quate, and T. W. Kenny, "Process compatible polysilicon-based electrical through-wafer interconnects in silicon substrates," *J. Microelectromech. Syst.*, vol. 11, pp. 631–640, 2002.

- [12] J. H. Wu, J. Scholvin, J. A. del Alamo, and K. A. Jenkins, "A Faraday cage isolation structure for substrate crosstalk suppression," *IEEE Microwave Wireless Comp. Lett.*, vol. 11, pp. 410–412, May 2001.

- [13] J. H. Wu, J. Scholvin, and J. A. del Alamo, "An insulator-lined silicon substrate-via technology with high aspect ratio," *IEEE Trans. Electron Devices*, vol. 48, pp. 2181–2183, Dec. 2001.

- [14] A. A. Ayón, R. Braff, C. C. Lin, H. H. Sawin, and M. A. Schmidt, "Characterization of a time multiplexed inductively coupled plasma etcher," *J. Electrochem. Soc.*, vol. 146, pp. 339–349, 1999.

- [15] Y. Shacham-Diamand, A. Dedhia, D. Hoffstetter, and W. G. Oldham, "Reliability of copper metallization on silicon-dioxide," in *Proc. Int. IEEE VLSI Multilevel Interconnection Conf.*, 1991, pp. 109–115.

- [16] G. M. Adema, L.-T. Hwang, G. A. Rinne, and I. Turlik, "Passivation schemes for copper/polymer thin-film interconnections used in multichip modules," *IEEE Trans. Comp., Hybrids, Manufact. Technol.*, vol. 16, pp. 53–59, Jan. 1993.

- [17] E. P. van de Ven, I.-W. Connick, and A. S. Harrus, "Advantages of dual frequency PECVD for deposition of ILD and passivation films," in *Proc. Int. IEEE VLSI Multilevel Interconnection Conf.*, 1990, pp. 194–201.

- [18] C.-K. Hu and J. M. E. Harper, "Copper interconnections and reliability," *Mater. Chem. Phys.*, vol. 52, pp. 5–16, 1998.

- [19] T. R. Anthony, "Forming electrical interconnections through semiconductor wafers," J. Appl. Phys., vol. 52, pp. 5340–5349, 1981.

- [20] M. E. Goldfarb and R. A. Pucel, "Modeling via hole grounds in microstrip," *IEEE Microwave Guided Wave Lett.*, vol. 1, pp. 135–137, Feb. 1991.

- [21] T. Blalack, Y. Leclercq, and C. P. Yue, "On-chip RF isolation techniques," in *Proc. IEEE BCTM*, 2002, pp. 205–211.

- [22] K. Joardar, "Signal isolation in BICMOS mixed mode integrated circuits," in *Proc. IEEE BCTM*, 1995, pp. 178–181.

- [23] I. Rahim, B.-Y. Hwang, and J. Foerstner, "Comparison of SOI versus bulk silicon substrate crosstalk properties for mixed-mode ICs," in *Proc. IEEE Int. SOI Conf.*, 1992, pp. 170–171.

- [24] J.-P. Raskin, A. Viviani, D. Flandre, and J.-P. Colinge, "Substrate crosstalk reduction using SOI technology," *IEEE Trans. Electron Devices*, vol. 44, pp. 2252–2261, Dec. 1997.

- [25] S. Stefanou, J. S. Hamel, P. Baine, M. Bain, B. M. Armstrong, H. S. Gamble, M. Kraft, and H. A. Kemhadjian, "Ultralow silicon substrate noise crosstalk using metal Faraday cages in an SOI technology," *IEEE Trans. Electron Devices*, vol. 51, pp. 486–491, Mar. 2004.

- [26] J. H. Wu and J. A. del Alamo, "An equivalent circuit model for a Faraday cage substrate crosstalk isolation structure," in *Proc. IEEE Radio Frequency Integrated Circuits Symp.*, 2004, pp. 635–638.

**Joyce H. Wu** received the B.S. degree in electrical engineering from the University of Michigan, Ann Arbor, in 1996 and the M.S. degree in electrical engineering from the Massachusetts Institute of Technology (MIT), Cambridge, in 2000, where she is currently pursuing the Ph.D. degree in electrical engineering, and where her research focuses on through-wafer interconnect technologies for mixed-signal circuits.

From 1996 to 1998, she worked at Intel Corpo-

ration as a failure-analysis engineer. She has also worked at Toshiba Corporation, Yokohama, Japan, and the Hitachi Central Research Laboratory, Tokyo, Japan.

**Jörg Scholvin** received the S.B. and M.Eng. degrees in electrical engineering from the Massachusetts Institute of Technology (MIT), Cambridge, in 2001, where he is currently pursuing the Ph.D. degree in electrical engineering, and carrying out research on RF power CMOS technology.

Jesús A. del Alamo received the degree in telecommunications from the Polytechnic University of Madrid, Madrid, Spain, in 1980, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, in 1983 and 1985, respectively. At Stanford University he carried out his Ph.D. dissertation on minority carrier transport in heavily doped silicon.

From 1977 to 1981 he was with the Institute of Solar Energy, Polytechnic University of Madrid, working on silicon solar cells. From 1985 to 1988

he was Research Engineer with Nippon Telegraph and Telephone-LSI Laboratories, Atsugi, Japan, where he conducted research on III-V heterostructure field-effect transistors. Since 1988, he has been with the Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology (MIT), Cambridge, where he is currently a Professor. His current research interests are on Gigahertz power transistors, including Si LDMOS on SOI, RF power CMOS, GaAs PHEMTs and InP HEMTs. He is also active in online laboratories for science and engineering education.

Dr. del Alamo was awarded the Baker Memorial Award for Excellence in Undergraduate Teaching at MIT in 1992. In 1993, he received the H. E. Edgerton Junior Faculty Achievement Award at MIT. In 1999, he was elected a Corresponding Member of the Royal Spanish Academy of Engineering. In 2001, he received the Louis D. Smullin Award for Excellence in Teaching and the Class of 1960 Innovation in Education Award, both at MIT. In 2002, he received the Amar Bose Award for Excellence in Teaching from MIT. In 2003, he was selected as a MacVicar Faculty Fellow at MIT. From 1991 to 1996, he was an NSF Presidential Young Investigator.