# Enhancement-mode BEOL In<sub>2</sub>O<sub>3</sub> FETs with Record Logic Performance: Experiments and Compact Modeling

Yanjie Shao<sup>1\*</sup>, Dylan Ma<sup>2</sup>, Dimitri A. Antoniadis<sup>1</sup>, Lan Wei<sup>2</sup>, and Jesús A. del Alamo<sup>1</sup>

<sup>1</sup>Microsystems Technology Laboratories, MIT, Cambridge, MA 02139, USA, \*email: <a href="mailto:shaoyj@mit.edu">shaoyj@mit.edu</a>

<sup>2</sup> Department of Electrical and Computer Engineering, University of Waterloo, Waterloo, ON, N2L3G1, Canada

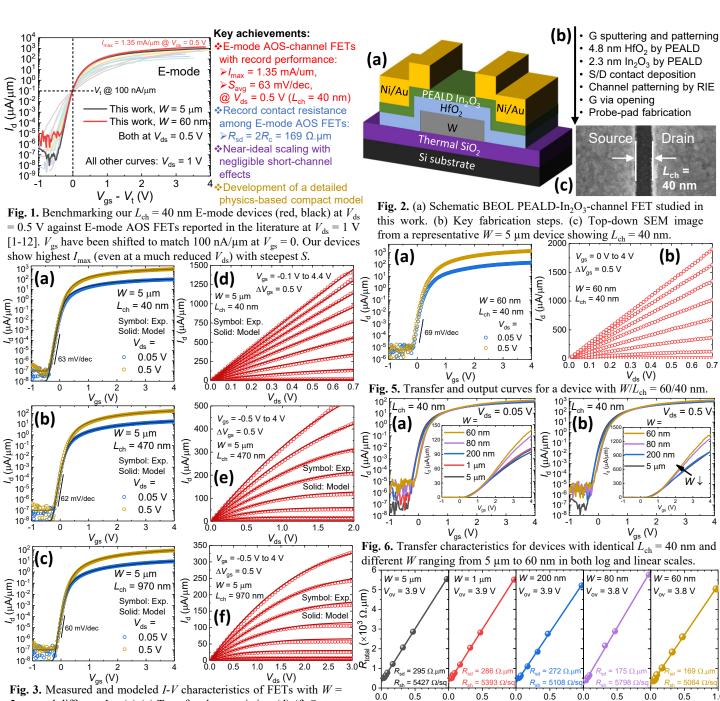

Abstract—We demonstrate record logic performance in backend-of-the-line (BEOL)-compatible enhancement-mode (Emode) amorphous oxide semiconductor (AOS) field-effect transistors (FETs). These devices exhibit near-ideal scalability down to 40 nm in channel length ( $L_{ch}$ ). Using an  $In_2O_3$  channel by plasma-enhanced atomic-layer deposition (PEALD), we achieve E-mode operation in  $L_{ch} = 40$  nm devices with a maximum drive current ( $I_{max}$ ) of 1.35 mA/ $\mu$ m, a peak transconductance  $(g_{m,peak})$  of 490  $\mu$ S/ $\mu$ m, and a close-tothermal-limit average room-temperature subthreshold swing  $(S_{\text{avg}})$  of 63 mV/dec, all at a drain-to-source voltage  $(V_{\text{ds}})$  of 0.5 V. A total source (S) and drain (D) resistance ( $R_{sd}$ ) of 169 E-mode record-low among AOS-FETs, demonstrated. Capacitance-voltage (C-V) characteristics reveal different threshold voltages  $(V_t)$  in the intrinsic channel and in the S/D to gate (G) overlap regions. We develop a physics-based MVS-AOS model which accurately captures the essential physics at play in our experimental devices, including C with frequency dispersion in the S/D region. This work advances state-of-the-art BEOL AOS-FET technology, and paves the way for future design-technology co-optimization (DTCO) on this promising device platform for BEOL monolithic 3D integration.

## I. INTRODUCTION

AOSs have emerged as promising channel material candidates for BEOL monolithic 3D integration, thanks to large-area low-thermal-budget processing capability, decent electron mobility ( $\mu_e$ ), and ultralow leakage current [1-12]. Especially, In<sub>2</sub>O<sub>3</sub>-channel FETs have demonstrated impressive performance [13]. However, they generally display depletionmode (D-mode) operation with  $V_t < 0$  [12-14]. Many emerging applications such as 1T1C and 2T0C embedded dynamic random-access memory (eDRAM) desire high-performance Emode FETs to achieve long retention, fast switching, and high energy efficiency [15]. Recently, we have demonstrated Emode BEOL FETs based on a PEALD-In<sub>2</sub>O<sub>3</sub> channel [16]. This earlier work as well as that of other authors, however, suffered from relatively poor scalability. The full potential of this novel device technology and the development of a physically meaningful compact model have yet to be realized.

In this work, we have fabricated nanoscale PEALD-In<sub>2</sub>O<sub>3</sub> FETs and carried out systematic I-V and C-V characterization together with compact modeling. We have achieved record logic performance among any E-mode AOS FETs [1-12] (**Fig.** 1), including record-high  $I_{\rm max}=1.35$  mA/ $\mu$ m and  $g_{\rm m,pk}=490$   $\mu$ S/ $\mu$ m at  $V_{\rm ds}=0.5$  V with a near-ideal  $S_{\rm avg}=63$  mV/dec and a record-low  $R_{\rm sd}=169$   $\Omega.\mu$ m in  $L_{\rm ch}=40$  nm devices. We demonstrate near-ideal  $L_{\rm ch}$  scaling with negligible short-channel effects (SCEs) down to 40 nm, the smallest  $L_{\rm ch}$  in this work. A compact model (MVS-AOS) has been formulated following classic drift-diffusion theory that includes quantum effects. Our model accurately captures key device operation

features over the entire range of  $L_{\rm ch}$ , including intrinsic and extrinsic C-V behavior, as well as bias-dependent  $\mu_{\rm e}$  and  $R_{\rm sd}$ .

#### II. DEVICE FABRICATION

Schematic device structure and key fabrication steps are shown in Figs. 2(a)-(b). We adopted a tungsten (W) gate by sputtering, a 4.8-nm-thick  $HfO_2$  gate insulator by PEALD at 250 °C, a 2.3-nm-thick  $In_2O_3$  channel by PEALD at 150 °C, and a Ni/Au bilayer for S/D contact. Channel isolation was done with a Cl-based reactive-ion etching (RIE) process. Our devices feature channel widths (W) ranging from 5  $\mu$ m to 60 nm and  $L_{\rm ch}$  ranging from 970 nm to 40 nm. Fig. 2(c) shows an SEM image of a representative device with  $L_{\rm ch}=40$  nm.

### III. ELECTRICAL CHARACTERISTICS

**Fig. 3** shows transfer and output characteristics of FETs with W = 5 μm and different  $L_{\rm ch}$ . Linear turn-on in all the devices indicates good Ohmic contacts [**Figs. 3(d)-(f)**]. In the  $L_{\rm ch} = 40$  nm device [**Fig. 3(a)**], a nearly ideal  $S_{\rm avg} = 63$  mV/dec over three decades of drain current ( $I_{\rm d}$ ) is obtained at both  $V_{\rm ds} = 0.05$  and 0.5 V with negligible drain-induced barrier lowering (DIBL).  $I_{\rm max} > 1$  mA/μm is obtained at  $V_{\rm ds} = 0.5$  V in this device [**Fig. 3(d)**]. Remarkable  $S_{\rm avg}$  down to the thermionic limit, 60 mV/dec, is observed over two decades of current in long-channel devices [**Fig. 3(c)**], suggesting a very high-quality metal-oxide-semiconductor (MOS) interface.

Transfer characteristics of a set of  $W=5~\mu m$  devices with different  $L_{\rm ch}$  in both log and linear scales at  $V_{\rm ds}=0.05$  and 0.5 V are shown in **Fig. 4**. Again, for all the devices,  $S_{\rm avg}$  approaches 60 mV/dec. The tight  $V_{\rm t}$  distribution highlights the excellent electrostatic scaling in our transistors.

We have further characterized devices with different W down to 60 nm. Fig. 5 shows transfer and output characteristics of a transistor with W=60 nm and  $L_{\rm ch}=40$  nm. In this device,  $I_{\rm max}=1.35$  (1.9) mA/ $\mu$ m is obtained at  $V_{\rm ds}=0.5$  (0.7) V together with  $S_{\rm avg}=69$  mV/dec, a value limited by the instrument noise floor. Fig. 6 shows W scaling leads to substantial improvement in  $I_{\rm max}$  with a slight positive  $V_{\rm t}$  shift and little  $S_{\rm avg}$  degradation.

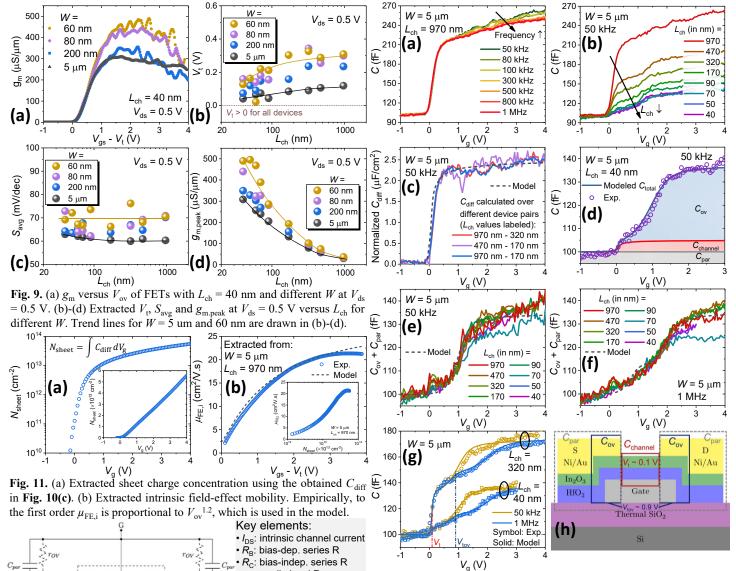

We have performed gated transmission line method (G-TLM) measurements for multiple values of  $L_{ch}$  and W (Fig. 7). Total resistance ( $R_{\text{total}}$ ) is extracted at  $V_{\text{ds}} = 0.05 \text{ V}$  and varying gate overdrive ( $V_{ov} = V_{gs} - V_t$ ).  $V_t$  is defined at a constant 4 nA×  $W/L_{\rm ch}$ , corresponding to 100 nA/ $\mu$ m @  $L_{\rm ch}$  = 40 nm. Examples of  $R_{\text{total}}$  vs.  $L_{\text{ch}}$  at  $V_{\text{ov}} = 3.8$ , 3.9 V are shown in Fig. 7 where good linear dependences are demonstrated. This enables us to extract channel sheet resistance  $(R_{sh})$  and unit-width  $R_{sd}$ . We observe a clear decrease of both  $R_{\rm sd}$  and  $R_{\rm sh}$  as  $V_{\rm ov}$  increases (**Fig. 8**). This is due to an increase in  $\mu_e$  as sheet carrier concentration ( $N_{\text{sheet}}$ ) increases, as will be shown later. A clear decrease of  $R_{\rm sd}$  is also seen with decreasing W, while  $R_{\rm sh}$ remains nearly W-independent. This suggests that intrinsic channel properties ( $N_{\text{sheet}}$  and  $\mu_{\text{e}}$ ) are likely independent of W, while the S/D regions become more conductive in narrower devices, likely induced by mechanical strain. Further study of strain effect is required. Remarkably, a record-low  $R_{\rm sd}=169$   $\Omega.\mu{\rm m}$  is achieved at W=60 nm suggesting a transfer length  $(L_{\rm T})$  of ~30 nm. Such a short  $L_{\rm T}$  highlights the highperformance potential in E-mode PEALD-ln<sub>2</sub>O<sub>3</sub> FETs with a scaled contact length.

Fig. 9 presents the scaling behavior for key figures-of-merit at  $V_{\rm ds} = 0.5$  V. Fig. 9(a) graphs  $g_{\rm m}$  characteristics for  $L_{\rm ch} = 40$ nm devices with different W as a function of  $V_{ov}$ . At a low  $V_{ov}$ < ~0.5 V, all the curves overlap, indicating intrinsic-channeldominated electron transport. As Vov increases, gm saturation appears first in wider devices leading to a lower  $g_{m,peak}$  limited by the higher  $R_{\rm sd}$ . We obtain a high  $g_{\rm m,peak} = 490 \ \mu \rm S/\mu m$  at  $V_{\rm ds}$ = 0.5 V in the  $W/L_{ch}$  = 60/40 nm device. Figs. 9(b) and 9(c) show excellent SCE as  $L_{\rm ch}$  scales down but a slightly positive  $V_{\rm t}$  shift and a minor  $S_{\rm avg}$  degradation as W scales down. This is attributed to the steepest slope region of the *I-V* characteristics not being resolved in narrow-W devices due to limited instrument resolution. The scaling of  $g_{m,peak}$  [Fig. 9(d)] clearly demonstrates the gradual transition of channel-limited transport at long  $L_{\rm ch}$  to  $R_{\rm sd}$ -limited current at short  $L_{\rm ch}$ . At  $L_{\rm ch} = 970$  nm, all the devices display nearly identical  $g_{m,peak}$ , while at  $L_{ch} = 40$ nm, clear increase of  $g_{m,peak}$  is visible as W decreases.

To understand charge-control physics, we characterized C-V behavior in W = 5 um devices, the same set as shown in **Figs.** 3 and 4. S/D were shorted during the measurements. Fig. 10(a) shows mild frequency dispersion of C for the  $L_{ch} = 970$  nm device. The frequency-independent C at low  $V_{\rm g}$  when the device turns on from full depletion to weak accumulation indicates a nearly trap-free MOS interface, aligning well with the observed  $S_{\text{avg}} = 60 \text{ mV/dec.}$  Fig. 10(b) shows 50-kHz C-V curves for devices with varying  $L_{ch}$ . All the curves converge to a nearly constant C at negative bias, likely originating in the fullydepleted S/D contact regions, as well as bias-independent pad parasitics. Thanks to a nearly  $L_{ch}$ -insensitive  $V_t$  as shown in Fig. **8(b)**, we can extract intrinsic channel C through normalized differential C ( $C_{\text{diff}}$ ) between several pairs of devices with different  $L_{ch}$ . Despite unavoidable noise due to the very small Cmagnitude, reproducible  $C_{\text{diff}}$  results are obtained [Fig. 10(c)] corresponding to a capacitance equivalent thickness (CET) of  $\sim$ 1.4 nm. With this result, we can then study  $L_{\rm ch}$ -independent Ccomponents. This includes a bias-dependent overlap  $C(C_{ov})$ originating from accumulation and depletion in the S/D regions, as well as a bias-independent parasitic  $C(C_{par})$ . Taking the  $L_{ch}$ = 40 nm device as an example, we show the split of Ccomponents in Fig. 10(d). Bias-dependent  $C_{ov}$  dominates in this short device. This explains the nearly saturated C-V curves in Fig. 10(b) when  $L_{\rm ch} \le 70$  nm. We have further extracted  $C_{\rm ov}$  +  $C_{par}$  at 50 kHz and 1 MHz, showing  $L_{ch}$ -independent behavior at both frequencies [Fig. 10(e)-(f)]. Minor variation is due to the unavoidable process uncertainty in the fabrication. An interesting finding from this C analysis is that  $V_t$  in the S/D regions  $(V_{tov})$  is ~0.9 V, substantially more positive than the channel  $V_t$  of ~0.1 V. Examining the frequency dispersion of C-V, we find that it is almost  $L_{ch}$ -independent in magnitude [Fig. 10(g)] and it suddenly appears at ~0.9 V. This strongly suggests that prominent trapping effect is taking place in the S/D regions, as opposed to the intrinsic channel.

We summarize the unique physics of our devices in Fig. 10(h) that suggests a lower doping level under the contacts. This observation might explain the excellent  $L_{ch}$  scaling of SCE

in our devices in contrast with other Ni-contacted  $In_2O_3$  FETs with severe  $V_t$  roll-off ascribed to oxygen-scavenging-induced heavier doping in the Ni-contacted S/D regions [17].

From the *I-V* and *C-V* characteristics, we calculate  $N_{\rm sheet}$  by integrating  $C_{\rm diff}$  as shown in **Fig. 11(a)**. We then extract intrinsic field-effect mobility ( $\mu_{\rm FE,i}$ ) using the linear-regime transfer characteristics of the  $W/L_{\rm ch} = 5~\mu {\rm m}/970~{\rm nm}$  device [**Fig. 11(b)**], obtaining a peak  $\mu_{\rm FE,i}$  of 21.5 cm<sup>2</sup>/(V.s).

## IV. MVS-AOS MODELING AND DEVICE PHYSICS

A physics-based compact model (MVS-AOS) is developed following the equivalent circuit in **Fig. 12** and key equations listed in **Fig. 13**. The basic current and charge in the intrinsic regions [Eqs. (1)-(3)] are formulated following the classic drift-diffusion theory used in [18]. Additional effects critical to AOS FETs are implemented on top of the basic model, including (i) quantum effects [19] in both channel and S/D regions, (ii) Coulomb scattering limited effective mobility, (iii)  $C_{\rm ov}$  with frequency dispersion and (iv) bias-dependent  $R_{\rm sd}$  and  $C_{\rm ov}$ . In  $R_{\rm sd}$  =  $2(R_{\rm B} + R_{\rm C})$ ,  $R_{\rm B}$  decreases with  $V_{\rm gs}$  due to decreasing Coulomb scattering. The frequency dispersion in  $C_{\rm ov}$  is captured by adding  $r_{\rm ov}$  (**Fig. 12**). A coefficient of 1.2 is used for empirically modeling the power-law  $V_{\rm ov}$  dependence of both  $\mu_{\rm FE,i}$  and  $1/R_{\rm B}$ .

Modeled vs. experimental I-V and C-V characteristics are shown in **Fig. 3** and **Fig. 10**, respectively. Excellent accuracy across all  $L_{ch}$  is achieved, validating that correct physics are captured. Channel current, even at  $L_{ch} = 40$  nm, appears to be mobility-limited (rather than saturation-velocity-limited) over the range of measured  $V_{ds}$ . Our modeling results emphasize the importance of parasitic engineering in short- $L_{ch}$  AOS-FETs.

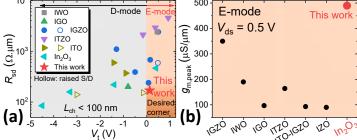

Finally, we benchmark  $R_{\rm sd}$  vs.  $V_{\rm t}$  for short- $L_{\rm ch}$  AOS FETs, as well as maximum  $g_{\rm m,peak}$  achieved in each AOS material with E-mode FET operation at  $V_{\rm ds} = 0.5$  V (**Fig. 14**). Our devices show significant performance improvement in the on-state and exhibit the lowest  $R_{\rm sd}$  when compared to any E-mode AOS-based FETs [1-12,14-16,20-27].

## V. CONCLUSIONS

This work demonstrated an E-mode BEOL AOS-FET technology with record logic performance and excellent scalability. Our comprehensive study reveals unique physics under the contacts. An MVS-AOS compact model has been developed that accurately describes transistor behavior over the entire dimensional range. Our results should be instrumental in facilitating future high-performance AOS-FET development for BEOL monolithic 3D integration.

### ACKNOWLEDGMENT

This work was supported by SRC (#3140.001) and Intel Corporation through MIT AI HW Program. Device fabrication was carried out at MTL and MIT.nano facilities of MIT.

# REFERENCES

[1] Q. Li, IEDM, 22.7.1, 2022. [2] D. Zheng, IEDM, 4.3.1, 2022. [3] K. Chen, VLSI, 298, 2022. [4] K. A. Aabrar, IEDM, 2023. [5] Y.-K. Liang, IEDM, 2023. [6] J. Zhang, IEDM, 2023. [7] J.-C. Chiu, VLSI, 17-3.1, 2023. [8] S. Hooda, VLSI, T17-1.1, 2023. [9] Z. Wu, EDL, 45, 408, 2024. [10] Q. Lin, IEDM, 2024. [11] K. A. Aabrar, VLSI, 2024. [12] S. Lee, VLSI, 2024. [13] M. Si, VLSI, T2-4.1, 2021. [14] C. Niu, IEDM, 2023. [15] K. Toprasertpong, VLSI, T11-4.1, 2023. [16] Y. Shao, IEDM, 2024. [17] J.-Y. Lin, TED, 72, 3004, 2025. [18] U. Radhakrishna, TED, 66, 95, 2019. [19] S. Rakheja, TED, 62, 2786, 2015. [20] J. Zhang, VLSI, T17-2.1, 2023. [21] Y. Kang, VLSI, T11-2.1, 2023. [22] C. Gu, EDL, 44, 837, 2023. [23] S. Wahid, IEDM, 12.5.1, 2022. [24] W. Chakraborty, VLSI, TH2.1, 2020. [25] K. Han, TED, 68, 6610, 2021. [26] J. Zhang, EDL, 44, 273, 2023. [27] J.-Y. Lin, IEDM, 2024.

0.5

$L_{ch}$  ( $\mu m$ )

0.0

0.5

$L_{ch}$  ( $\mu$ m)

0.0

Fig. 3. Measured and modeled I-V characteristics of FETs with W = 5  $\mu$ m and different  $L_{ch}$ : (a)-(c) Transfer characteristics, (d)-(f) Output characteristics. The MVS-AOS model (Section IV) shows good accuracy and scalability.

10<sup>2</sup>  $W = 5 \mu m$  $W = 5 \mu m$ 10 10<sup>2</sup> (a) 10<sup>1</sup> 10<sup>0</sup> = 40 to 970 nm = 40 to 970 nm 10 (m<sup>1</sup>/<sub>2</sub> 10<sup>-1</sup>) 10<sup>-2</sup> 10<sup>-3</sup> (m/km) 10<sup>-1</sup> 10<sup>-2</sup> 10<sup>-3</sup>  $V_{\rm ds} = 0.05 \, \text{V}$ = 0.5 V€10<sup>-4</sup> .⊽10<sup>-</sup> 10-10-10-10<sup>-</sup> 10 V<sub>gs</sub> (V) 10 V<sub>gs</sub> (V) 10 10 0 2  $V_{gs}(V)$

$L_{ch}$  ( $\mu$ m)

**Fig. 7.** Gated-TLM analysis of FETs with different W. Symbols: exp. data;

0.0

0.5

$L_{\rm ch}$  ( $\mu m$ )

0.5

$L_{\rm ch}$  ( $\mu m$ )

Fig. 4. Transfer characteristics for FETs with  $W=5~\mu m$  and  $L_{\rm ch}$  Fig. 8. (a)  $R_{\rm sd}$  and (b)  $R_{\rm sh}$  as a function of gate overdrive for devices with ranging from 40 to 970 nm at (a)  $V_{\rm ds}=0.05~{\rm V}$  and (b)  $V_{\rm ds}=0.5~{\rm V}$ . different  $W_{\rm sd}$ , extracted using gated-TLM analyses as shown in Fig. 7. The Both log and linear scales are shown. A tight  $V_t$  distribution with nearbias-dependent component of  $R_{\rm sd}$  ( $R_{\rm B}$  in Fig. 12) is found to be proportional ideal S for all  $L_{\rm ch}$  values demonstrates excellent electrostatic scaling.

Fig. 12. Netlist for MVS-AOS formulation.  $I_{DS}$ ,  $C_{GS}$  and  $C_{GD}$  scale with  $L_{ch}$  following classic drift-diffusion theory.  $R_{B}$ ,  $R_{C}$ ,  $C_{ov}$  (S,D) and  $C_{par0}$  are attributed to the S/D regions, hence independent of  $L_{ch}$   $r_{ov}$  (proportional to trap time constant) is a small-signal resistance to capture the C-V frequency dispersion due to the inertia of charge responding to high frequency signal in the trap-rich S/D regions.

$r_{ov}$ : small-signal R

C<sub>G(S,D)</sub>: intrinsic channel C

$$\begin{aligned} &Q_{i(S,D)} = C_{inv} \cdot 2n\varphi_T \ln\left(1 + \exp\left(\frac{V_{GX(Si,Di)} - V_i}{2n\varphi_T}\right)\right) & (1) \quad I_{DS} = \mu \frac{W}{L} \frac{(Q_{cS}^2 - Q_{cD}^2)}{2C_{inv}} & (2) \quad S = n\varphi_T \ln(10) & (5) \\ &Q_{(S,D)} = \frac{2WL}{(Q_{cS}^2 - Q_{cD}^2)^2} \left[\mp Q_{i(D,S)}^2 \frac{Q_{cS}^3 - Q_{cD}^3}{3} \pm \frac{Q_{cS}^3 - Q_{cD}^3}{5}\right]; \quad C_{G(S,D)} = -\frac{\partial Q_{(S,D)}}{\partial V_{G(S,D)}} & (3) \quad \mu_{FE,i} \propto V_{ov}^{\theta_{FE}} & (6) \\ &Q_{ov(S,D)} = WC_{ovQB} \cdot n_{ov}\varphi_T \ln\left(1 + \exp\left(\frac{V_{G(S,D)} - V_{i,ov}}{n_{ov}\varphi_T}\right)\right); \quad C_{ov(S,D)} = \frac{\partial Q_{ov(S,D)}}{\partial V_{G(S,D)}} & (4) \quad R_B \propto V_{ov}^{\theta_{FE}} & (7) \end{aligned}$$

**Fig. 13.** Key equations for MVS-AOS.  $Q_{i(S,D)}$ : areal charge density at the (S,D) edge of the channel following [18].  $φ_T$ : thermal voltage. S: subthreshold swing.  $C_{inv}$ : areal gate capacitance in the channel, including quantum effects [19].  $V_t$  is the threshold voltage accounting for DIBL and trap-induced  $V_t$  shift.  $Q_{(S,D)}$ : S/D terminal charge.  $θ_{(FE,R)}$  are fitting parameters.  $C_{ov(S,D)}$  is computed similarly as  $Q_{i(S,D)}$  with threshold voltage  $V_{tov}$  and includes the quantum effects through  $C_{ovQB}$ . Almost identical parameter set is used to fit devices with different  $L_{ch}$  at W=5 μm, with only minor adjustment of the S, DIBL,  $V_t$  and the unit-width overlap capacitances used to calculate  $C_{ovQB}$ .

**Fig. 14**, Benchmarking of (a)  $R_{\rm sd}$  vs.  $V_{\rm t}$  for short- $L_{\rm ch}$  AOS FETs and (b) Maximum  $g_{\rm m,peak}$  achieved at  $V_{\rm ds}=0.5$  V in E-mode FETs made of each AOS material [1-12,14-16,20-27].  $V_{\rm t}$  is defined @ 100 nA/ $\mu$ m.