#### Accelerating the next technology revolution

# InAs Quantum-Well MOSFET with Record High $g_m$ , $f_T$ and $f_{max}$

**T.-W. Kim**, R. Hill, C. D. Young, D. Veksler, L. Morassi, S. Oktybrshky<sup>1</sup>, J. Oh, C. Y. Kang, D.-H. Kim<sup>2</sup>, J.A. del Alamo<sup>3</sup>, C. Hobbs, P.D. Kirsch, and R. Jammy

<sup>1</sup>CNSE, <sup>2</sup>Teledyne, <sup>3</sup>MIT

#### **Outline**

Introduction

Device design and process technology

Device results from logic to microwave characteristics

Conclusions

#### Possible Logic Technology Roadmap Ge pMOS; **ULP TFET Manufacturing Development Pathfinding** III-V nMOS 2021 2019 HINSEMATECH STech-Run01 Ge pMOS; Ge CMOS Si nMOS 2017 InGaAs 2015 SEMATECH III-V p-i-n TFET SEMATECH SiGe Si FinFET 2012 10 nm 2<sup>nd</sup> Gen HKMG Si 2009 HKMG **Channel Material** 2007 Si Intel **Junctions** Intel, Doping Intel **Manufacturability** 45nm 32nm 22nm 10nm 7nm 5nm 14nm

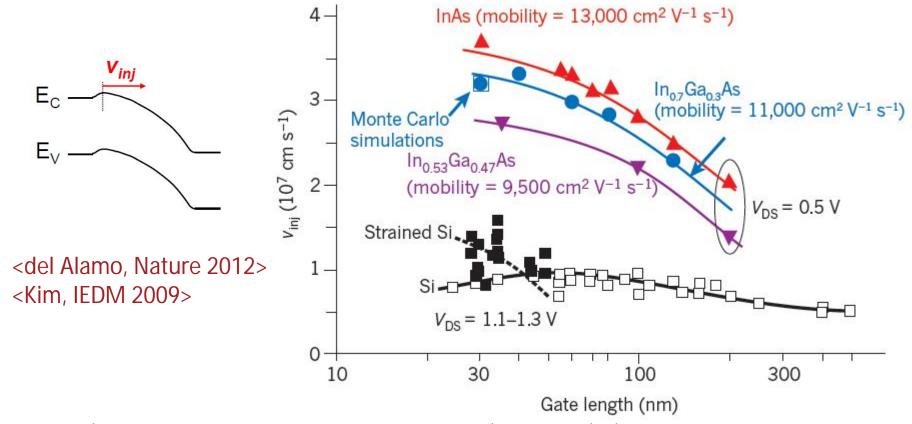

#### Motivation for InAs vs. InGaAs

- $v_{inj}$  (InAs>In<sub>0.7</sub>Ga<sub>0.3</sub>As/In<sub>0.53</sub>Ga<sub>0.53</sub>As) >  $2v_{inj}$ (Si) at less than half  $V_{DD}$

- Derived v<sub>inj</sub> values consistent with quasi ballistic transport (Collision-free)

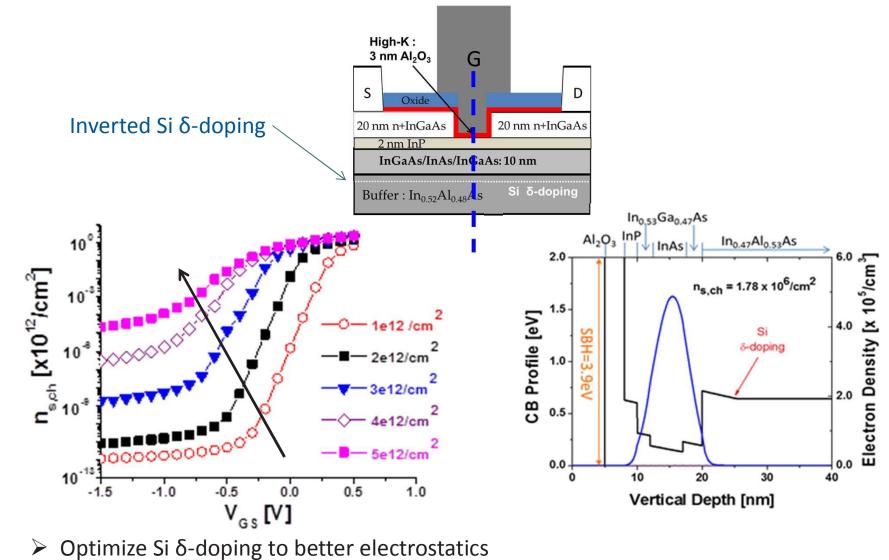

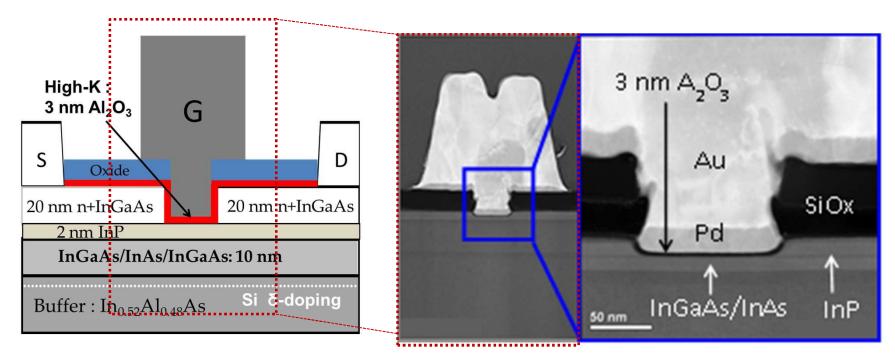

#### Layer structure with inverted Si $\delta$ -doping

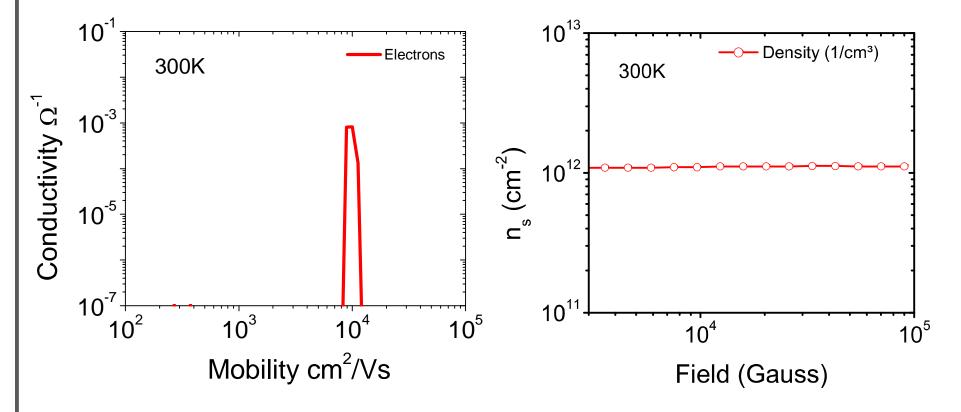

#### Validation of epi quality in this work

QMSA results from calibration structure

- $\mu_{n,Hall} = 11,200 \text{ cm}^2/\text{V-sec}$  and  $n_{s,ch} = 1 \text{ x } 10^{12}/\text{cm}^2$  at 300K

- $\mu_{n,Hall} = 20,000 \text{ cm}^2/\text{V-sec}$  and  $n_{s,ch} = 1 \text{ x } 10^{12}/\text{cm}^2$  at 77K

#### Test Structure Design

#### Unique features of this work:

- InAs channel for better transport

- Inverted Si  $\delta$ -doping for low excess  $R_{SD}$  and excellent electrostatic control

- 3 nm Al<sub>2</sub>O<sub>3</sub>/2 nm InP gate stack to improve D<sub>it</sub>

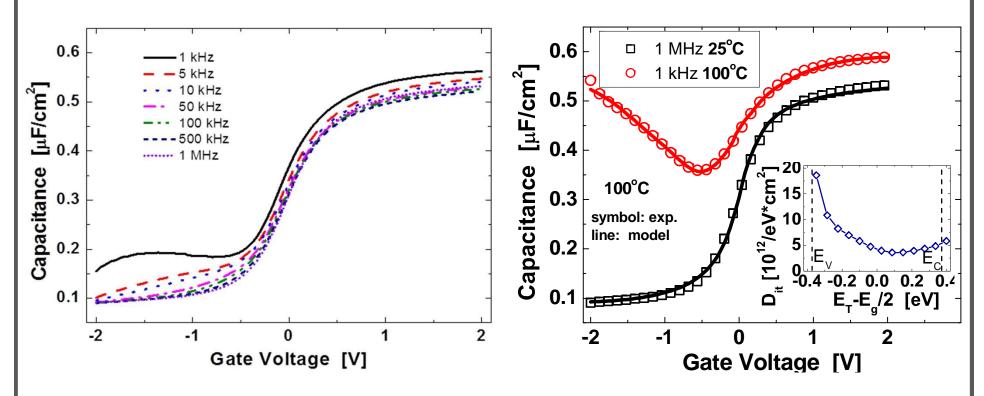

## SEMATECH Generalized Technique<sup>1)</sup> for D<sub>it</sub>

- Low frequency dispersion in both accumulation and depletion region

- $D_{it} = 4 \times 10^{12} / eV.cm^2$  from temperature High-Low frequency and Terman  $D_{it}$  extraction method

1) M. Madan, DRC, p. 117 (2011)

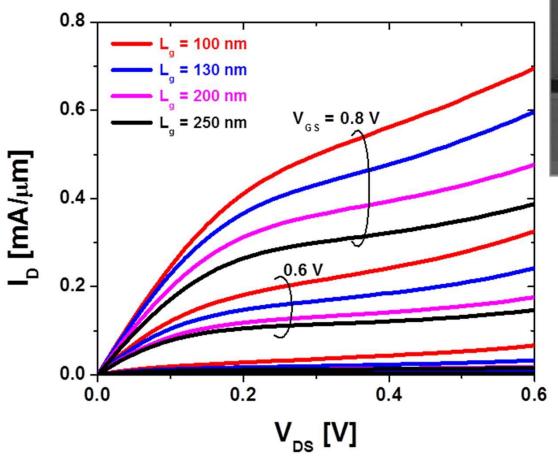

#### InAs MOSFET Output Characteristics

Optimized gate recess with L<sub>side</sub> < 5 nm

- Excellent I<sub>D</sub> saturation and pinch off behavior

- $I_{D,sat} = 0.68 \text{ A/mm at } V_{DS} = 0.6 \text{ V at } L_g = 100 \text{ nm}$

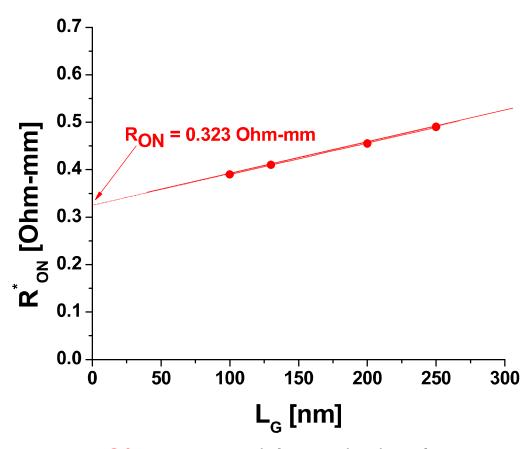

### R<sub>ON</sub> Characteristic

- R<sub>ON</sub> = 0.323 Ohm-mm with optimized gate recess process (L<sub>side</sub> < 5 nm)</li>

- R<sub>ON</sub> could be reduced with self-aligned architecture

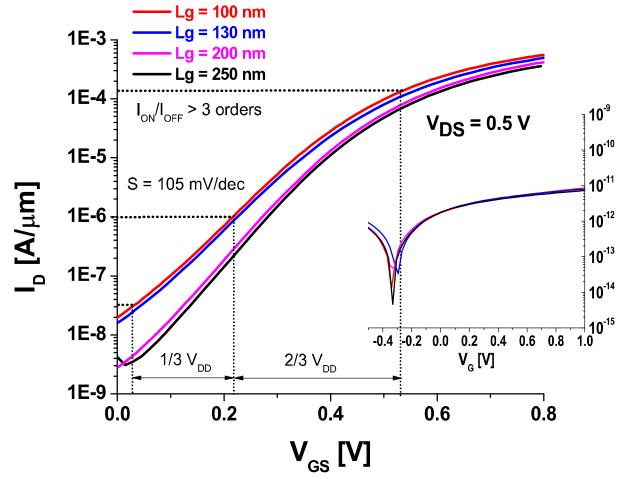

#### InAs MOSFET Subthreshold Characteristics

- SS = 105 mV/dec. at  $L_q$  = 100 nm with  $D_{it}$  = 4 x 10<sup>12</sup> /eV.cm<sup>2</sup>

- Excellent gate leakage → A room for EOT scaling below 2 nm

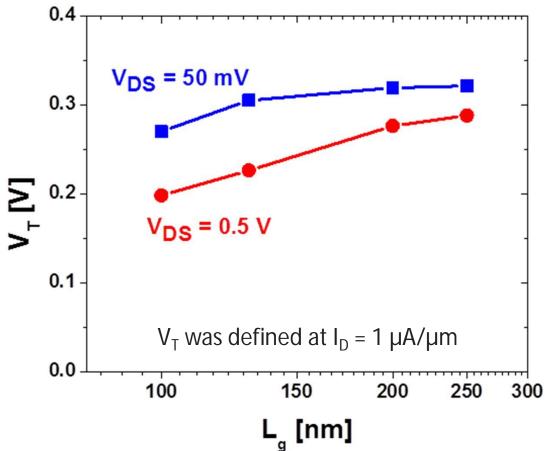

## V<sub>T</sub> roll-off

■ V<sub>T</sub> = 0.2 V at L<sub>q</sub> = 100 nm: Enhancement-mode operation

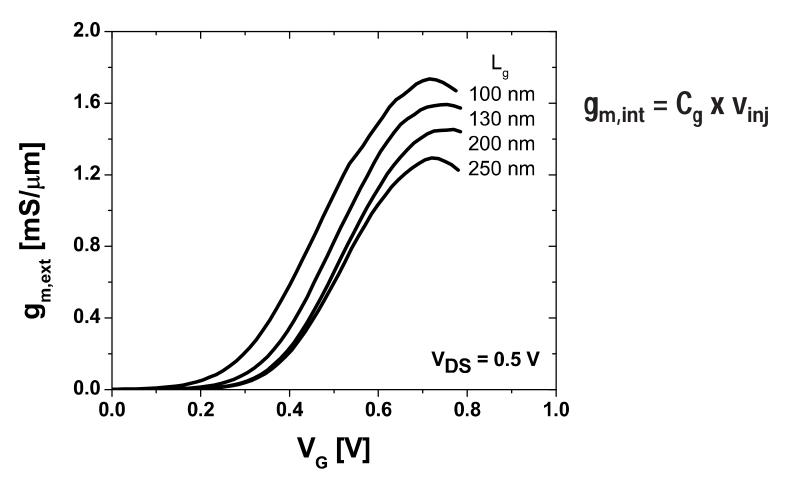

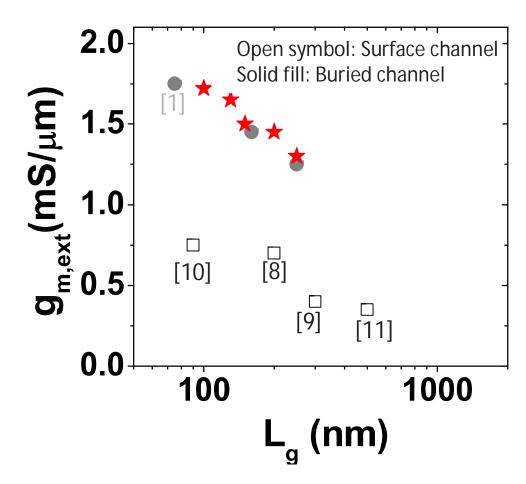

## InAs MOSFET g<sub>m</sub> Characteristic

$g_m = 1.73$  mS/ $\mu$ m at  $V_{DS} = 0.5$  V (A record  $g_{m,ext}$  at  $L_g = 100$  nm)

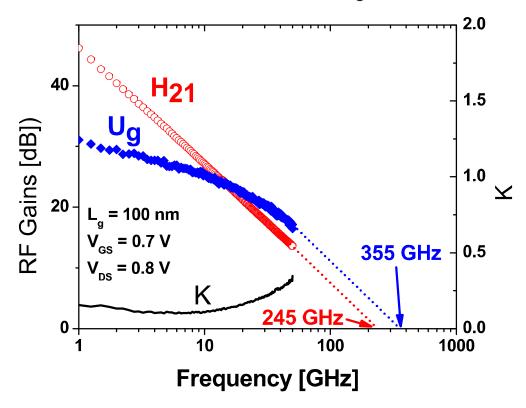

#### InAs MOSFET Microwave Characteristic

Calibration: LRRM, De-embedding: OPEN/SHORT

- L<sub>g</sub> = 100 nm: f<sub>T</sub> = 245 GHz & f<sub>max</sub> = 355 GHz at V<sub>DS</sub> = 0.8 V

→ These f<sub>T</sub> & f<sub>max</sub> are record values for any III-V MOSFET

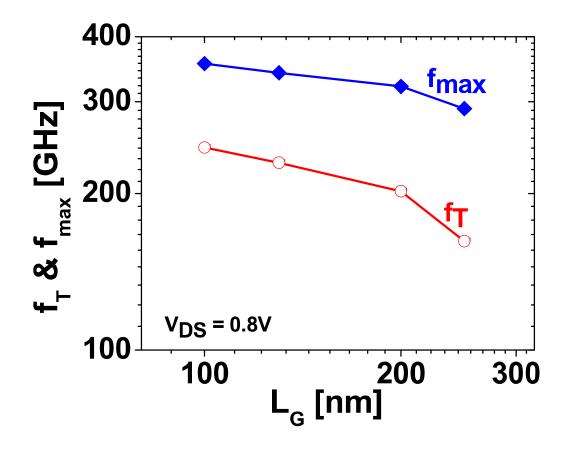

#### InAs MOSFET promising for RF Applications

- $L_g = 200 \text{ nm}$ :  $f_T > 200 \text{ GHz & } f_{max} = 300 \text{ GHz at V}_{DS} = 0.8 \text{ V}$

- Excellent performance for millimeter wave applications

#### III-V MOSFET Benchmarking

- A record transconductance at L<sub>g</sub> = 100 nm for III-V MOSFET

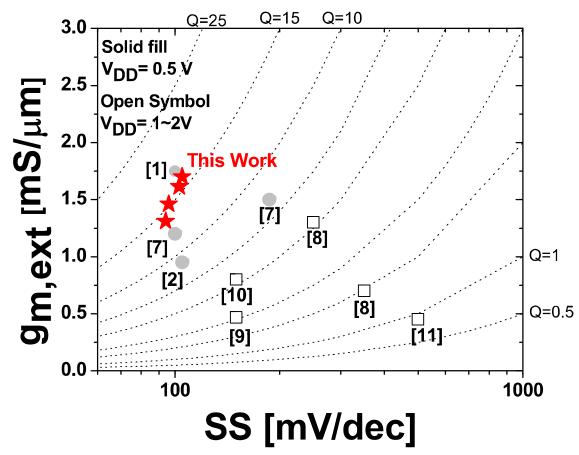

#### III-V MOSFET Q Benchmarking

- FOM Q factor defined as  $g_m/S$  Q = 16 for  $L_g$  = 100 nm and  $V_{DD}$  =0.5 V.

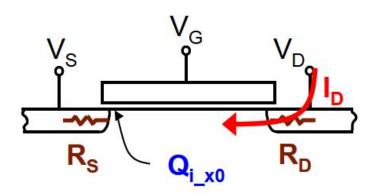

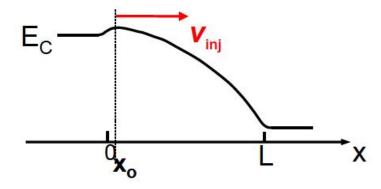

## Extraction methodology for v<sub>inj</sub>

Kim, IEDM 2009

$$I_D = Q_{i\_x0} \times V_{inj} \Rightarrow V_{inj} = \frac{I_D}{Q_{i\_x0}}$$

- I<sub>D</sub>: measured drain current

- Q<sub>i x0</sub>: sheet-charge density

$$Q_{i_x0} = \int C_{gi} dV_{GS,i}$$

with

$$C_{qi}$$

@  $V_{DS}$  = 10 mV

- C<sub>qi</sub> extracted from S-parameters

- R<sub>S</sub> and R<sub>D</sub> correction:

$$V_{DSi} = V_{DS} - I_{D} \times (R_{S} + R_{D})$$

$$V_{GSi} = V_{GS} - I_{D} \times R_{S}$$

- V<sub>T</sub> roll-off correction

- DIBL correction

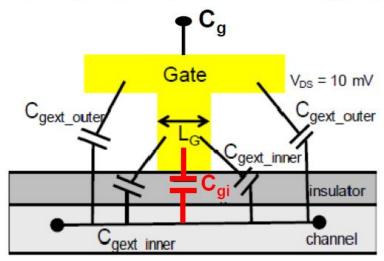

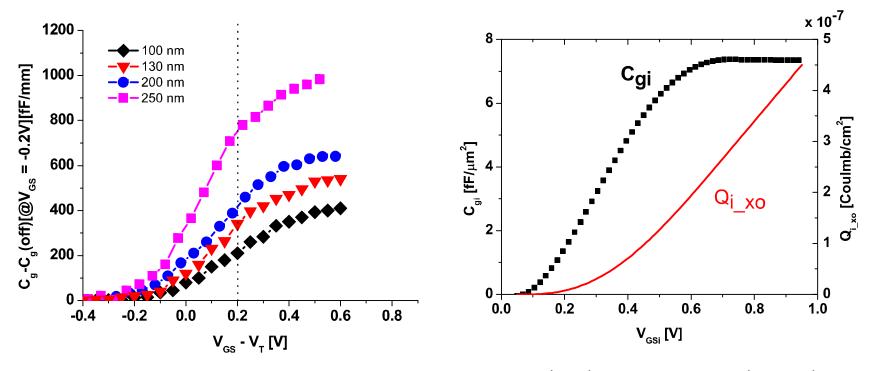

# C<sub>gi</sub> - How to extract in small L<sub>g</sub> device

$C_{gi} \rightarrow \text{intrinsic gate capacitance per unit area [fF/<math>\mu m^2$ ]} (from S-parameters at linear region,  $V_{DS} = 10 \text{ mV}$ )

$$C_{g} = C_{gi} \times L_{g} + 2C_{gext\_inner} + 2C_{gext\_outer} \times C_{g} @ OFF$$

$$\propto f(V_{GSi} - V_{T})$$

$$\rightarrow C_{g} - C_{g}(OFF) = C_{gi} \times L_{g} + 2C_{gext\_inner}$$

$Q_{I_{-xo}}$  - How to extract

$$\mathbf{Q_{i_x0}} = \int \mathbf{C_{gi}} d(V_{GS,i})$$

, where  $\mathbf{C_{gi}} \otimes V_{DS} = 10 \text{ mV}$

- Extracted intrinsic gate capacitance ( $C_{gi}$ ) & charge ( $O_{i\_xo}$ ) in channel with S-parameter

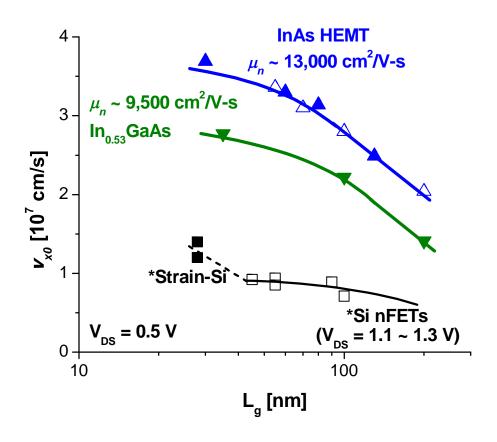

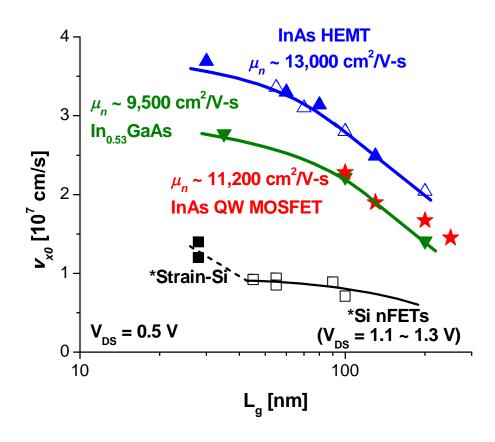

## Benchmarking: Injection velocity (v<sub>inj</sub>)

- InAs MOSFET shows 2 X higher  $v_{inj}$  than Si, even at  $V_{DS} = 0.5 \text{ V}$

- Consistent V<sub>inj</sub> depending on channel mobility

## Benchmarking: Injection velocity (v<sub>inj</sub>)

- InAs MOSFET shows 2 X higher v<sub>ini</sub> than Si, even at V<sub>DS</sub> = 0.5 V

- Consistent V<sub>ini</sub> depending on channel mobility

#### Conclusions

- InAs (rather than In<sub>x</sub>Ga<sub>1-x</sub>As) enables:

- Record  $g_m = 1.73$  mS/ $\mu$ m at  $V_{DS} = 0.5$  V

- No significant  $I_{OFF}$  penalty (S = 105 mV/dec)

- $-2 \times V_{inj}$  improvement vs. s-Si

- First rigorous v<sub>inj</sub> benchmarking shows InAs MOSFET competitive with best known HEMT

| InAs MOSFET (0.5V)         | InAs HEMT (0.5V)           | Strained Si MOSFET (1V)  |

|----------------------------|----------------------------|--------------------------|

| 2.3 x 10 <sup>7</sup> cm/s | 2.8 x 10 <sup>7</sup> cm/s | 1 x 10 <sup>7</sup> cm/s |