Our Research

The sheer number and diversity of IoT devices, along with their limited resources, makes IoT security a challenge quite different from securing traditional computing systems.

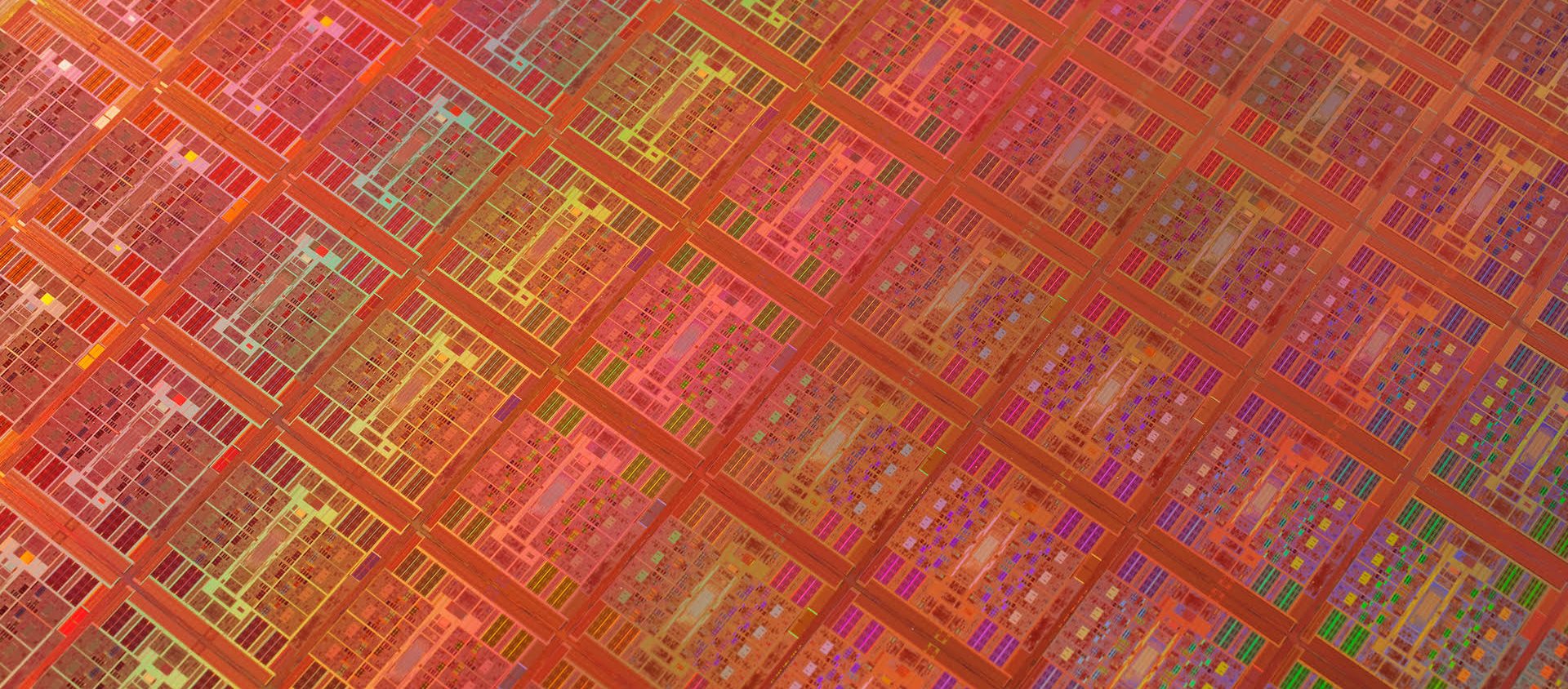

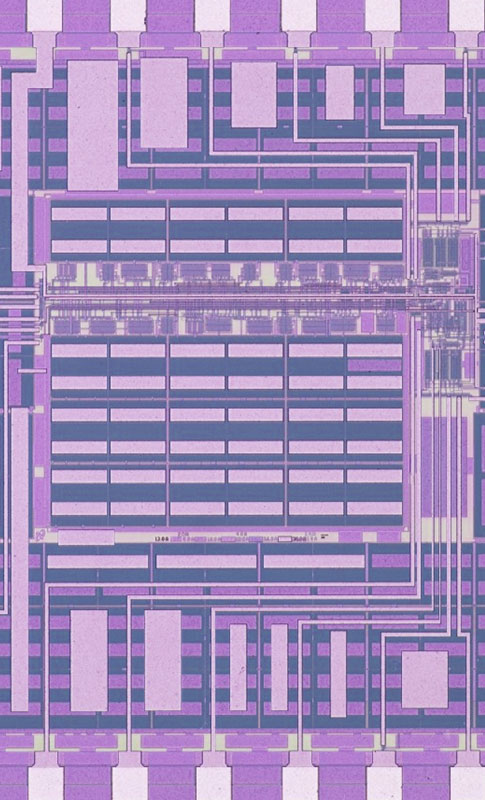

Research spans across multiple levels of abstraction ranging from innovative new process technologies and circuit styles to architectures, algorithms, and software technologies.

Our group’s approach to biomedical electronics starts with developing a deep understanding of physiological or biological processes, which leads to new insights on how to develop an energy-efficient implementation of the system.

In the News

Aug 11, 2022

M. I. W. Khan, J. Woo, X. Yi, M. Ibrahim, R. Yazicigil, A. Chandrakasan and R. Han, Best Student Paper Award, 1st Place, 2021 IEEE Radio Frequency Integrated Circuits Symposium, "A 0.31THz CMOS Uniform Circular Antenna Array Enabling Generation/Detection of Waves with Orbital-Angular Momentum," Jun. 2021.

Aug 11, 2021

Kyungmi Lee, Anantha P. Chandrakasan, the Bob Owen's Best Student Paper Award, 2021 IEEE Workshop on Signal Processing Systems (SiPS), "Understanding the Energy vs. Adversarial Robustness Trade-Off in Deep Neural Network", 2021.

Dec 29, 2021

SSCS Member Aya Amer was one of the 2020 SSCS Predoctoral Award Recipients. In this video, Aya offers advice to students and young professionals.