## Software Tools for Process-Sensitive Reliability Assessments of IC Designs

## Personnel

S. M. Alam, D. E. Troxel, and C.V. Thompson

## Sponsorship

MARCO Focused Research Center on Interconnect (MARCO/DARPA)

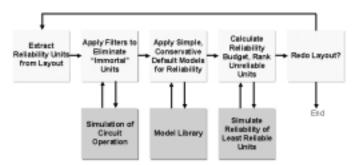

Integrated circuits are often designed using simple and conservative 'design rules' to ensure that the resulting circuits will meet reliability goals. This simplicity and conservatism leads to reduced performance for a given circuit and metallization technology. To address this problem, we had developed a TCAD tool, ERNI, which allows process-sensitive and layout-specific reliability estimates for fully laid out or partially laid out integrated circuits (Figure 10).

Circuit-level reliability analyses require reliability assessment of a large number of sometimes complexly connected interconnect trees. We have shown through modeling and experiments that the resistance saturation observed in straight via-to-via Al lines, which can lead to immunity from electromigration-induced failure, also occurs in more complex interconnect trees. We have also shown that trees will be 'immortal' if their effective current-density line-length product, (jL)<sub>eff</sub>, is below a critical value. The jL product that defines immortality can be determined from experimental characterization or simulation of the reliability of straight via-to-via lines. Simple tests for tree immortality can be used in a hierarchical way to eliminate trees from further more computationally intensive reliability assessments. After filtering of immortal trees, the reliability of mortal trees must be assessed. This can be done through reliability simulations with individual trees, but this computationally intensive method should be reserved for the most problematic trees, those with the least reliability, and which are least convenient to 'fix' through layout modifications. We have suggested computationally simple and conservative 'default' models for assessment of tree reliabilities based on the Korhonen analysis and have tested models and simulations through experiments on simple interconnect trees.

Recent development in semiconductor processing technology has enabled the fabrication of a single integrated circuit with multiple device-interconnect layers or dice stacked on each other. This approach is commonly

Fig. 10: A flowchart for a full hierarchical circuit-level reliability assessment, the basis for the prototype tool ERNI.

referred to as the three-dimensional or 3D integration of ICs. Although there has been some research on the impact of 3D integration on chip size, interconnect delay, and overall system performance, reliability issues in the 3D interconnect arrays are fairly unknown. We have extended the reliability concepts in ERNI and developed a framework for reliability analysis in 3D circuits with a novel Reliability Computer Aided Design (RCAD) tool, ERNI-3D. Using ERNI-3D, circuit designers can get interactive feedback on the reliability of their circuits associated with electromigration, 3D bonding, and joule heating.

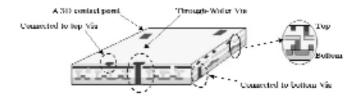

As 3D integration technology is not yet widespread, and no CAD tool supports IC layouts for such a technology, we first developed a comprehensive 3D-circuit layout methodology. The circuit on each wafer or device-interconnect layer can be laid out separately with inter-wafer via information embedded in the layout. The inter-wafer via information is generalized into three categories sufficient for defining all types of interconnection between wafers in a 3D stack (Figure 11). A strategy for layout-file management that incorporates the orientation of each wafer in the bonding process was also developed. We have implemented the layout methodology in 3D-MAGIC, an extension of MAGIC originally developed at UC Berkeley and widely used in academia. Test circuits designed with 3D-MAGIC include a 3D 8-bit adder and an 8-bit encryption processor mapped into a 3D FPGA.

Fig. 11: Different types of via/contact for 3D ICs.

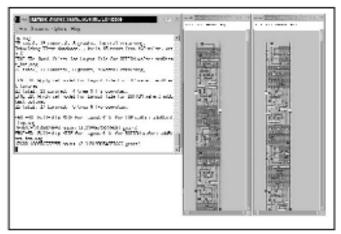

The reliability CAD tool, ERNI-3D, parses 3D circuit lavouts and extracts both conventional and 3D interconnect trees. It employs the Hierarchical Reliability Analysis approach, and filters out a group of immortal trees using their current-density length products. After the filtering process, more accurate, but more computation-intensive reliability models are applied to the remaining interconnect trees to compute their median and mean times to failures. Finally, all the different times to failures are combined using a joint probability distribution to report a single reliability figure for the whole chip. This initial version of ERNI-3D treats 3D circuits with two wafers or device-interconnect lavers in the stack (see figure 12). However, the data-structures and algorithms in the tool are generic enough to make it compatible with 3D circuits with more than two device-interconnect layers and to allow the incorporation of more sophisticated reliability models in the future. Future work will also include modification of ERNI-3D to account for newly discovered differences in the geometry dependence of the reliability of Cu-based interconnects compared with Al-based interconnects.

*Fig.* 12: *Graphical User Interface of ERNI-3D. Here ERNI-3D is run on a 2-wafer 3D 8-bit Adder layout.*