## **Active Optical Clock Distribution**

**Personnel** T. Simpkins (A. P. Chandrakasan)

## Sponsorship

MARCO Focused Research Center on Interconnect (MARCO/DARPA) and NDSEG Fellowship

Clock distribution has become a major problem in integrated circuits. Although clock cycle times continue to decrease, the time allocated to uncertainty in the clock due to skew and jitter has remained constant. Therefore, the percentage of the clock budget devoted to uncertainty has become significant.

One solution to the clock uncertainty problem is to distribute the clock optically. Conventionally, this has involved using a transimpedance pre-amplifier to convert the optical current pulses from the photodetector into voltage waveforms. An inverter-based cascade is then used to amplify the clock pulses into full-swing signals that drive the local clock buffers. Past research has shown that this approach is limited by the imperfect matching of amplifiers from one block to another. Arising from process, voltage, and temperature, these variations can significantly increase the skew, thus negating the benefits of distributing a skewless optical clock.

Our research focuses on an alternative approach to optical clock distribution. Whereas the cascaded amplifier approach attempts to convert optical current pulses into an electrical waveform, our proposed architecture uses an optical reference clock to deskew an electrical clock. The architecture resembles that of a Delay-Locked Loop (DLL) in that a voltage-controlled delay line is used to synchronize the fully-buffered electrical clock with the optical current pulses from the photodetector. The use of a feedback-based architecture allows the loop to compensate for variations due to process, voltage, and temperature, and thus minimize skew.

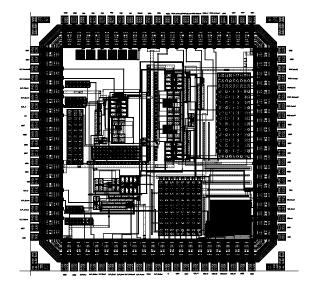

A test chip demonstrating this concept was fabricated using the TSMC .18  $\mu$ m process. The chip comprised three instances of the architecture, including both opened-loop and closed-loop versions. The photodetectors on the test chip were of the lateral PIN type and were implemented in standard CMOS, although the architecture is also compatible with other types. Finally, a low-resolution time-to-digital converter was included to measure the skew between the optical current input and the electrical clock output.

Fig.9: