## Ultra Wideband Radio

## Personnel

R. Blazquez and P. Newaskar (A. P. Chandrakasan)

## Sponsorship

La Caixa Fellowship and Presidential Fellowship

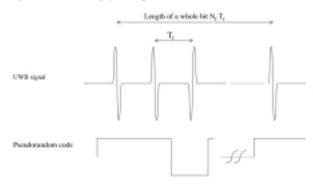

Recent approval by the Federal Communications Commission of Ultra-Wideband (UWB) Radio has rekindled interest in the development of this promising technology. This wireless system uses a bandwidth greater than 1 GHz to transmit information, while keeping the average transmitted power below the noise floor so as not to interfere with existing services that already use the same band. A typical UWB signal is a collection of narrow pulses (0.2 to 0.5 ns) with a very low duty cycle (1%) as shown in Figure 6. Each user is assigned a unique Pseudo-random Noise (PN) sequence that is used to encode the train of pulses, either in position or polarity. UWB radio offers high bit rates, low probability of interception and detection, precise locationing capability (stemming from the sub-nanosecond timing resolution) and the possibility of implementation using an exceedingly simple architecture.

Fig. 6: Structure of a UWB signal

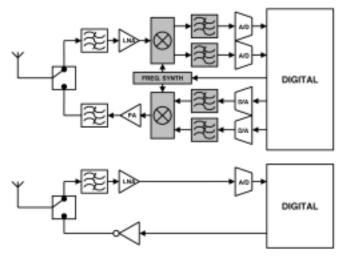

The goal of this project is the development of a novel transceiver architecture in which the signal is digitized as close to the antenna as possible. An "all-digital" architecture means low-cost, ease-of-design and all the associated benefits of CMOS technology scaling (Figure 7). Furthermore, it allows for full-programmability in terms of synchronization, signal processing and demodulation algorithms, thus approaching the vision of a software-configurable radio.

Architectural issues aside, there are some interesting circuit-level challenges that include high-speed, lowpower analog-to-digital conversion, low-jitter clocking, antenna co-design and pulse shaping.

Fig. 7: Architectural Comparison

As a first step in this project, a behavioral model of a UWB system is being developed in Matlab to understand and quantify the different trade-offs involved. The design of a prototype using discrete, off-the-shelf components and a test-chip are underway. We intend to eventually integrate the entire system on a single chip.