## SiGe-on-insulator (SGOI) Substrate Fabrication and Strained-Si *n*-MOSFET on SGOI

## Personnel

Z. Cheng, G. Taraschi, M. T. Currie, C. W. Leitz, A. J. Pitera and M. Lee (E. A. Fitzgerald, D. A. Antoniadis and J. L. Hoyt)

## Sponsorship

Singapore-MIT Alliance program and DARPA HGI

Relaxed SiGe-on-insulator (SGOI) substrate is a promising platform for various applications. On the SGOI substrate, for example, high mobility SiGe-based CMOS devices can be fabricated. By matching the lattice constant of the SiGe layer, III-V materials may also be integrated into SGOI substrates for various optoelectronic applications. In addition, the devices fabricated on SGOI structure have various benefits originated from the insulating configuration, such as high speed, better insulation, etc.

In this project, two approaches were developed for the fabrication of the relaxed SGOI substrates. Both methods incorporate wafer-bonding of SiGe/Si donor wafers (grown via UHV-CVD) to oxidized handle wafers. The first approach uses etch-back to remove the backside of the donor wafer, whereas the other method employs hydrogen-ion-implant-induced delamination to split the donor wafer.

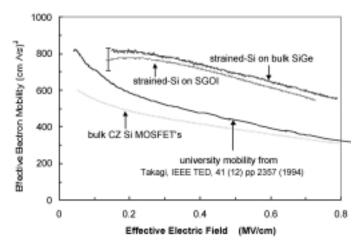

Strained-Si MOSFET's were fabricated on relaxed SGOI substrates with high Ge concentration of 25%. A thin strained Si layer was grown epitaxially on the relaxed SGOI substrates. The n-MOSFET's fabricated on this structure, with the strained Si layer as channel, shows significant electron mobility enhancement (1.7X) compared to both the co-processed bulk Si device and the universal mobility curve, as shown in the Figure 41.

Fig. 41: Measured effective electron mobility as a function of effective vertical electric field. The error bar represents the variation among devices. The measured effective electron mobility is significantly higher for MOSFET's fabricated on both SGOI and bulk SiGe, compared to both the universal mobility and that of the co-processed bulk Si MOSFET's.